文章编号:1671-4598(2025)09-0351-06

DOI:10.16526/j. cnki. 11-4762/tp. 2025. 09. 042

中图分类号:TP311

文献标识码:A

# 一种高可靠抗辐照定时器设计方法

## 马春阳,郭 玥,孝斯文

(南京电子技术研究所,南京 210039)

摘要:卫星等大型系统装备中,定时器是触发各单元协同工作的核心,定时器的精度和稳定性关乎着整个系统工作的成败;空间辐照效应特别是总剂量效应和单粒子效应,可能造成定时器产生的定时时序紊乱,影响整个系统工作异常;设计并实现了一种基于 FPGA 的高可靠抗辐照定时器;设计采用程序存储三取二、快速软件上注、定时刷新、关键参数异常保护、软件三模冗余、定时脉宽保护等技术,保障了定时器在空间辐照环境中的可靠运行;经实验验证,定时器软硬件抗辐照措施有效,满足卫星等大型系统对定时器高可靠抗辐照时序产生的要求。

关键词:定时器、抗辐照、三模冗余、FPGA

## A Design Approach for High-Reliability Radiation-Hardened Timer

MA Chunyang, GUO Yue, LI Siwen

(Nanjing Research Institute of Electronics Technology, Nanjing 210039, China)

Abstract: In large-scale systems such as satellites, timer is the key component for triggering synchronized operations across all units. The precision and stability of timer is critical to the success of the entire system. Space radiation effects, particularly Total Ionizing Dose (TID) effects and Single Event Effects (SEE), may induce timing sequence disruptions, consequently causing operational anomalies throughout the entire system. Designs and implements a high-reliability, radiation-hardened timer approach based on FPGA. Key techniques including triple modular redundancy (TMR) for program storage, rapid software uploading, periodic refresh, critical parameter anomaly protection, software TMR, and timing pulse-width protection were employed to ensure reliable operation of the timer in the space radiation environment. Experimental verification demonstrated that the radiation-hardening measures for both hardware and software in the timer are effective, fulfilling the stringent requirements for highly reliable, radiation-tolerant timing generation in satellites and other large-scale systems.

Keywords: Timer; Radiation-Hardened; TMR; FPGA

#### 0 引言

卫星等大型系统装备是由诸多功能不同的单元组成,各单元之间按照一定的时序相互配合,协同完成系统功能。定时器作为卫星系统的重要组成部分,产生系统所需的同步脉冲、上升下降沿等定时触发信号,控制各单元协同工作[1-5]。随着卫星工作方式日趋多样化,对定时时序的灵活性和精度要求越来越高。

国内外均开展了星上定时器的研究工作。为保证定时时序的可靠性,通常采用两种方案,一种是采用反熔丝 FPGA 或 ASIC 等一次性编程器件承担定时时序产生功能,其具备高可靠的特点,但因芯片内部资源限制,无法满足复杂定时时序产生的要求;另外一种是基于高性能 FPGA 架构,以高精度系统时钟作为定时节拍器,

接收外部输入的定时参数表,基于比较器原理产生既定的定时时序并输出,可产生复杂定时序并实现对各单元ns级精度的灵活控制<sup>[6-9]</sup>,为提高定时器高可靠配置加载的能力,采用一次性烧写芯片存储工作程序,使得定时器不具备功能重构的能力,影响卫星系统在轨功能完善和迭代。

本文设计了一种基于 FPGA 架构的星上定时器,核心部件主要是 FLASH 存储器和 SRAM 型 FPGA,FLASH 存储器用于存储 FPGA 配置程序,可实现配置程序的灵活重构,SRAM 型 FPGA 可实现系统定时时序产生和输出。FLASH和 FPGA 内部的存储单元对空间辐照环境较为敏感,在轨运行过程中,FLASH 存储器的存储区可能被单粒子打翻(即内容由 0 变为 1,或由 1 变为 0),长时间工作甚至因总剂量效应存在芯片

收稿日期:2025-08-25; 修回日期:2025-09-01。

作者简介:马春阳(1990-),男,硕士,工程师。

引用格式:马春阳,郭 玥,李斯文.一种高可靠抗辐照定时器设计方法[J]. 计算机测量与控制,2025,33(9):351-356.

失效风险; FPGA 用于存储关键定时参数的用户寄存器 同样存在位翻转风险,从而导致定时器产生的定时时序 异常,影响系统工作[10-16]。为保证定时器在轨产生稳定 可靠的定时时序, 需对定时器开展软件和硬件高可靠抗 辐照设计。

#### 定时器原理

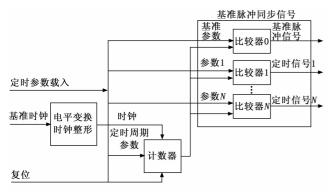

定时器原理如图 1 所示, SRAM 型 FPGA 将外部 高精度基准时钟通过时钟整平的方式产生 FPGA 所需 的定时基准时钟,根据定时周期参数,产生本地高精度 周期计数器。结合基准定时参数和以基准定时为参照的 其他定时参数,利用比较器方法,产生系统所需的基准 脉冲信号和其他定时信号,如图2所示,定时信号1/ 2/3 均以基准定时为参考产生。

图 1 定时产生原理框图

图 2 几种定时信号示意图

通常情况下, 定时周期参数和定时参数根据系统需 求,存放在 FPGA 寄存器或外围存储器当中,当定时 器开机后,会按照预定的定时参数值产生定时时序。这 种定时产生的方式灵活性不足,若需要更改定时时序, 就必须重新对 FPGA 内的定时参数进行烧写。为了适 应复杂系统对定时时序的灵活控制, 定时器采用参数化 定时产生技术,将与系统定时时序相关的定时参数,例 如脉冲周期、脉冲间隔、脉冲宽度等,均由外部软件实 现,并作为 FPGA 定时产生模块的输入。

利用参数化定时产生技术,定时器产生的定时时序 具备定时精度高、脉冲间隔、脉冲周期和脉冲宽度灵活 可控的特点,通过周期性改变定时参数,可灵活控制系 统各单元协同工作,从而实现系统不同工作模式的快速 无缝切换。

第 33 卷

### 2 空间辐照效应对定时器的影响

辐射环境由太阳活动产生的各种粒子组成,包括带 电粒子如电子、质子和重离子等,以及电磁辐射(光 子)如X射线、伽马射线或紫外线等,这些粒子部分 会对卫星各单元产生辐照效应, 主要包括总剂量效应 (TID) 和单粒子效应 (SEE) 两种。总剂量效应具备损 伤累积的特点,随着时间的推移,可导致器件永久性损 坏;单粒子效应主要分为单粒子翻转效应(SEU)和单 粒子闩锁效应 (SEL), 单粒子翻转效应不会导致硬件 损伤,但会在系统工作过程中打翻寄存器、存储器内的 数据,对系统任务产生一定影响;单粒子闩锁效应会造 成器件产生瞬时大电流,可能会导致器件烧毁[17-22]。

定时器核心电路主要为存储器和 FPGA 芯片。存 储器大多采用选用具备抗辐照能力的 NOR FLASH, FPGA 大多选用高性能抗辐照的 SRAM 型 FPGA, 空 间辐照效应对 FPGA 和 FLASH 在一定条件下均有较大 的影响。总剂量效应在长期工作积累后,可能导致 FLASH 芯片损伤,直接影响 FPGA 的程序配置和刷 新,导致定时器工作异常。单粒子效应可能会造成 FLASH 和 FPGA 内的用户存储区发生位翻转,导致与 定时时序产生相关的参数读取错误,造成定时时序未按 照预期的方式产生,严重情况下可导致整个星上系统工 作异常甚至永久性损伤。

#### 3 抗辐照定时器设计方法

本文从硬件和软件两方面设计了一种定时器,其采 用程序存储三取二、快速软件上注、定时刷新、关键参 数异常保护、软件三模冗余、定时脉宽保护等手段,实 现在空间辐照环境下定时时序的稳定输出,或在单粒子 翻转等异常工况下,关闭错误定时触发,防止对系统造 成不可逆的损害。

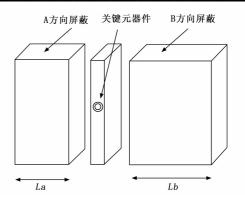

#### 3.1 硬件设计

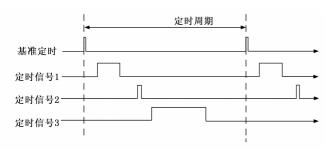

基于对定时器产生原理和空间辐照对定时器造成的 影响分析,设计了一种基于 SRAM 型 FPGA 的定时器 硬件电路,原理框图如图3所示。核心元器件包括 NOR FLASH、反熔丝 FPGA 和 SRAM 型 FPGA。

SRAM型 FPGA 实现时序产生功能; 3 片 NOR FLASH 分别存储相同的 SRAM 型 FPGA 配置程序; 1 片反熔丝 FPGA, 主要功能包括对 FLASH 芯片的读写 操作、对 SRAM 型 FPGA 配置刷新、对 FLASH 芯片 内数据状态监控, 以及通过快速上注通过实现对定时器 的软件上注。

反熔丝 FPGA 的同一地址线分别与 FLASH 芯片连 接,数据线相互独立。当同时读取3片FLASH的同一

图 3 基于 SRAM 型 FPGA 的定时器硬件原理框图

地址的数据时,会分别获得3个数据线上的有效数据,通过按位三取二的方式,比对得出正确数据,然后配置到 SRAM型 FPGA 运行。由于三片 FLASH 在同一位被同时打翻的可能性可以忽略不计,可确保 SRAM型 FPGA 配置的正确性。如果在三取二过程中发现3片 FLASH 中其中某1片与其他2片数据不一致,则说明FLASH 芯片内存储区发生了辐照影响,可通过状态监控功能上报异常遥测状态。

配置正确后,反熔丝 FPGA 以 10 s 为周期,定时 刷新 SRAM型 FPGA 的配置区,刷新过程无需中断用户功能,可进一步提高定时器硬件抗辐照能力。

定时器在轨长期运行过程中,3片FLASH存储芯片均有可能存在部分数据异常的情况,导致反熔丝FP-GA三取二数据错误,从而影响对SRAM型FPGA的配置刷新。本文定时器设计了快速软件上注通道,通过反熔丝FPGA的外部快速数据接口(例如LVDS接口,最大100Mbps的上注速率),完成对3片FLASH的写操作,实现对SRAM型FPGA功能的分钟级快速恢复和功能重构。

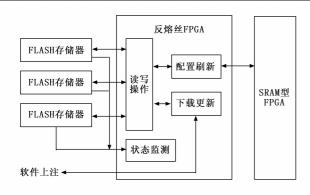

除了通过硬件电路设计本身,包括采用具备一定抗辐照能力的芯片实现定时器抗辐照外,还可以通过外部结构加固的方式增加定时器抗总剂量能力,评估定时器抗总剂量能力最重要的一个指标是芯片的 RDM ( Relative Damage Margin) 值,即相对损伤裕度。一般情况下,RDM 值大于 2 表示芯片的抗总剂量能力满足要求。定时器抗总剂量效应通过增加芯片外结构件等效铝厚度的方式处理。定时器结合自身所处卫星舱内环境特性,采用半空间分析法对抗总剂量能力进行评估。以需要估计辐射剂量的 PCB 为分界面,将设备内部结构对元器件的辐射屏蔽在 (A)、(B) 两个方向上划分为两个半空间,如图 4 所示。

例如,已知定时器 FLASH 芯片在 La 方向等效铝厚度为 X mm,在 Lb 方向等效铝厚度为 Y mm ,可结合卫星所在空间环境的深度剂量表得出 La 方向和 Lb

图 4 半空间法分析模型

方向的辐照剂量 Da Krad (Si) 和 Db Krad (Si),那么 FLASH 芯片所承受的总剂量为 (Da+Db) /2 Krad (Si)。假如该 FLASH 芯片抗总剂量指标为 Z Krad (Si),那么该器件在定时器中,RDM 值为 (Da+Db) / (2\*Z)。本文设计的定时器,主要芯片的 RDM 值均大于 2,满足抗总剂量指标要求。

通常情况下,除了以上程序存储三取二、快速软件 重构、定时刷新、结构加固等硬件抗辐照措施外,还会 采取主备冗余备份的方式增加定时器的在轨运行可靠 性。当主路定时器功能失效后,可外部控制切换至备份 定时器工作,主备定时器功能、接口完全冗余,仅需单 独切换定时器即可实现系统功能恢复。

#### 3.2 软件设计

硬件抗辐照设计实现了定时器对总剂量效应的防护能力,但对单粒子效应的防护,仅靠选用具备抗单粒子效应能力的元器件是远远不够的,甚至部分元器件的抗单粒子翻转能力远不满足空间辐照环境要求,例如高性能 SRAM 型 FPGA,由于芯片工艺原因,导致芯片本身抗单粒子翻转能力较弱。定时器在轨运行中,受到单粒子翻转效应影响,与定时时序产生相关的用户寄存器可能打翻,从而导致定时时序产生错误。

本文采用快速软件上注、关键软件三模冗余、关键 参数异常保护和定时脉宽输出保护等技术,从软件角度 实现高可靠抗辐照定时器设计。具体如下。

1) 快速软件上注:定时器设计了一种快速软件上注通道,采用 2 线制高速 LVDS 接口,数据传输速率最高可达 100 Mbps,实现了对 SRAM型 FPGA 的程序存储 FLASH 分钟级软件上注速率当 3 片 FLASH 芯片三取二失败后,可通过上注方式快速完成对定时器的状态恢复。具体上注步骤如下所示:

第一步:上位机通过 LVDS 通道向定时器的反熔 丝 FPGA 发送禁止对 SRAM 型 FPGA 刷新操作,防止此时 SRAM 型 FPGA 正在进行刷新操作,不响应擦除指令。执行完成后反熔丝 FPGA 向上位机返回状态寄

存器,确保禁止指令生效。该指令数据长度不大于 20 字节,数据链路传输时间和芯片执行指令的时间均为微秒量级,可忽略。上位机等待 5 ms,回读状态确保指令生效。

第二步:上位机通过 LVDS 通道向定时器反熔丝 FPGA 发送擦除指令,上位机发送 FLASH 擦除指令后,等待一定时间后读取状态信息,确认指令执行状态,等待时间与 FLASH 芯片扇区数、每个扇区擦除时间和擦除温度有关(低温时擦除速率慢)。

第三步: SRAM 型 FPGA 原始码流烧写。为保证数据传输成功率,定时器采用分帧上注技术,上位机将FPGA 的原始码流数据分为若干帧,逐帧传输。反熔丝FPGA 对数据帧进行合法性判断,包括数据包头、类型和校验和判断,判断正确后,同时写入3片 FLASH 中;

第四步:发送完全部上注数据帧后,发送 CRC 校验指令进行数据校验,验证写入 FLASH 的数据正确性,通过比较 FLASH 数据区的 CRC 和实际的 CRC值,判断写入 FLASH 数据的正确性并将状态信息反馈至上位机决策后续操作;

第五步:执行完上述操作并判断正确后,对定时器重启。向反熔丝 FPGA 发送从 FLASH 加载位流命令。等待反熔丝 FPGA 重新从 FLASH 配置 SRAM 型 FP-GA。查看 SRAM 型 FPGA 配置状态等状态信息判断最终上注是否执行成功。

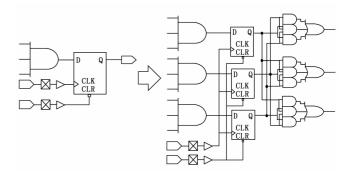

2) 关键软件三模冗余:识别定时器 FPGA 程序中涉及核心功能的子模块,例如定时时序产生模块等,采用 Precision Hi-Rel 三模工具对这些子模块进行局部三模加固设计。当其中一份发生位翻转时,仍可通过三取二方式实现正确的结果输出,同时上报位翻转信息状态。

Precision Hi-Rel 是 Mentor Graphics 在 NASA 指导下开发的一种基于综合的辐射效应缓解工具,该工具以verilog 输入,输出.v 网表文件的 TM 设计,能够支持对主流厂商的 FPGA 产品进行自动三模设计。Precision Hi-Rel 提供三种不同程度的 TMR 设计方法分别为 LT-MR、DTMR 和 GTMR。LTMR 仅对时序逻辑进行三模设计,对多数表决器单模设计;DTMR 对时序逻辑、组合逻辑以及多数表决器进行三模设计;GTMR 对时序逻辑、组合逻辑、多数表决器和全局缓冲器进行三模设计。由于多数表决器也存在被打翻的风险,且 GT-MR 对时钟也做了三模,增加了时钟偏移和抖动,会大幅降低工作频率和抖动,因此对定时器产生时序功能的SRAM 型 FPGA 关键模块的三模冗余设计采用 DTMR方式,如图 5 所示。

另外, Precision Hi-Rel 还可以进行安全状态机的

图 5 DTMR 方式三模设计

设置,具体包括 Basic Safe FSM、SEU Detect FSM 和 SEU Tolerant FSM。Basic Safe FSM 指当单粒子翻转进 人未定义状态时,使其恢复为初始状态;SEU Detect FSM 对状态机进行汉明编码,通过增加冗余编码进行 奇偶校验,判断翻转出错,该模式只能够探测翻转,不能进行纠正;SEU Tolerant FSM 模式能够对状态机编码的翻转进行汉明码的 EDAC 纠错。从系统最安全的 角度出发,SRAM 型 FPGA 的状态机设置选择 SEU Tolerant FSM 模式。

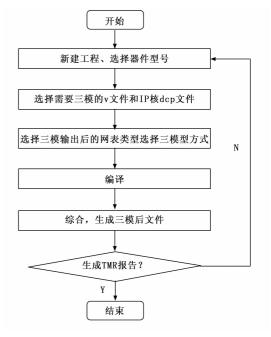

针对定时器 SRAM 型 FPGA 程序特点,采用按模块三模的方式,操作流程如图 6 所示。

图 6 SRAM 型 FPGA 三模操作流程图

在整个操作过程中,由于是按照模块进行三模,因此需要去掉 ADDIO 选项另外,针对 IP 核(支持部分常用 IP 核的三模),如果需要进行工具三模,需要将 IP 核的属性由 model 改为 optimize,并输入 setup design preserve-instantiated cells = false 指令。

软件三模冗余方式对 SRAM 型 FPGA 的资源有一

定的要求,图7、图8分别为三模前和三模后的资源消耗情况,从图中可以看出,三模后FPGA的LUT、FF和BRAM等资源使用率是三模前3倍。

| Resource | Utilization | Available | Utilization/% |

|----------|-------------|-----------|---------------|

| LUT      | 18906       | 203800    | 9. 28         |

| FF       | 18274       | 407600    | 4.48          |

| BRAM     | 50          | 445       | 11.24         |

| DSP      | 5           | 840       | 0.60          |

| 10       | 232         | 500       | 46. 40        |

| BUFG     | 7           | 32        | 21.88         |

| MMCM     | 1           | 10        | 10.00         |

图 7 软件三模前 FPGA 主要资源使用情况

| Resource | Utilization | Available | Utilization/% |

|----------|-------------|-----------|---------------|

| LUT      | 90910       | 203800    | 44.61         |

| FF       | 52662       | 407600    | 12.92         |

| BRAM     | 150         | 445       | 33.71         |

| DSP      | 5           | 840       | 0.60          |

| 10       | 232         | 500       | 46.40         |

| BUFG     | 7           | 32        | 21.88         |

| MMCM     | 1           | 10        | 10.00         |

图 8 软件三模后 FPGA 主要资源使用情况

关键软件三模冗余后,与 FPGA 性能相关的 LUT、BRAM、DSP 等资源使用率小于 80%,满足卫星平台对 FPGA 资源使用率的要求,对 FPGA 的运行速率、处理性能等无任何影响。

3) 定时参数异常保护和定时脉宽输出保护: 空间 辐照效应可能会造成定时器用于产生定时时序的定时参 数。设计一种定时参数异常情况下的保护功能,在定时 参数的传输不同阶段中,分别采用不同的手段进行异常 保护。①定时参数传输路径容错保护。定时器 SRAM 型 FPGA 与上位机的接口均采用校验(双字节异或校 验、单字节累加校验)方式,只有包头和数据校验正确 的数据才会被使用,校验错误的数据上报遥测;②RS (Reed-Solomon) 数据编解码。为防止定时参数在高速 链路传输过程中产生的异常翻转,采用 RS 数据编解 码技术,可实现每64字节纠正8字节错误;③阈值判 断。对关键定时参数如基准定时参数、周期定时参数、 定时脉冲宽度参数、定时脉冲数等参数进行合法性校 验。合理划分定时参数正常运行区间, 当出现定时参 数不在正常区间时,将该定时参数设置为缺省值,对 应的定时脉冲不输出,确保异常定时参数不会损伤系 统,同时上报异常状态信息,请求系统重新给定时器 发送合格的定时参数。④多次判断。针对定时器中涉 及部分定时时序是否产生的关键控制参数,要求用采 用双字节控制,且只有连续5次指令正确,才会切换 定时器内部的控制参数。

定时器产生定时时序后,需按照预定的节拍输出至各单元。部分定时时序以上升沿、下降沿的形式触发各单元工作,例如脉冲上升沿开始工作,下降沿停止工作,脉冲宽度决定了单元的工作时长。当定时时序的脉冲宽度因空间辐照影响产生异常超大脉宽时,导致单元长时间工作,从而引起单元损坏。采用定时脉宽保护机制,利用 FPGA 内部计数器对关键定时时序的脉冲宽度在定时器输出端进行采样并进行合法性判断,当脉冲宽度处于异常值时,关闭该定时时序的输出,防止定时器对相关系统单元造成误触发。

#### 3.3 测试验证

1) 抗总剂量效应试验:结合定时器硬件和软件抗辐照设计方法,开展了 Co60γ源的总剂量辐照试验。试验过程中分段逐级增加辐照剂量,分别观察定时器的加断电状态和工作状态信息。工作状态信息如图 9 所示,图中框内标注的数据含义为:第一个框内的 4 字节代表 FLASH 翻转的地址,正常情况下为 0x00000 \_ 0000,表示无地址翻转;第二个框内的 2 字节中的高字节代表被打翻的次数,正常情况下 0x00,表示无打翻次数;低字节中的高三位,代表被打翻的 FLASH 位号,若为 000b 表示未打翻、100b 表示第一片 FLASH 被打翻、010b 表示第二片 FLASH 被打翻、0x001b 表示第三片 FLASH 被打翻;111b 表示 3 片均不一致。正常情况下为 0x17,其高 3 位为 000b,代表 3 片 FLASH 均未被打翻。

00000000h: 00 01 93 0A 00 50 00 00 17 0D C1 DD FB FF CE 70 00000010h: 01 00 00 10 03 84 89 15 04 00 00 00 00 01 00000020h: 01 31 2E 31 2E 30 00 00 00 00 00 06 00 00 00 00 00000040h: 00 00 00 00 00 00 00 00 00 00 0.0 00 00 0.0 00000050h: 55 34 34 69 69 69 69 69 69 69 69 69 69 69 69 69 00000060h: 69 69 58 34 BE 94 7C 34 69 69 69 34 74 40 36 F3 00000070h: 00 FF FF 09 3F 00 00 01 00 00 0.1 AE 28 E1 01 00000080h: AC 81 BC AE 05 43 FF FF 00 00 00 00 09 8B 00000090h: 00 01 2B 8E 00 FF 00 17 01 10 01 10 00 00 000000a0h: 69 69 69 69 68 F4 F4 69 69 69 69 69 69 69 69 69 000000b0h: 68 69 69 69 68 69 68 69 69 69 69 69 69 69 000000c0h: 68 69 68 68 69 69 68 68 68 68 00 02 69 69 68 68 00000d0h: 68 69 69 69 68 68 68 68 68 68 69 000000e0h: 69 69 AA AA FF 00 01 01 00 01 02 03 04 05 06 07 000000f0h: 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 14 15 16 17

图 9 FLASH 正常状态信息

试验过程:采用剂量按阶梯递增的方式对定时器开展总剂量试验。分别在5、10、20、30、40、50和60 K总剂量下,对定时器进行照射,每阶段照射完成后,对定时器进行指标测试,测试完成后进入下一个指标测试。

试验结果: 当试验量级在 5~30 k 之间时,定时器工作正常、状态信息正常,未发生总剂量效应;当试验量级增加到 30~40 krad (Si) 时,三片 FLASH 中的一片失效,定时器可以正常实现三取二功能和定时时序产生。状态信息如图 10 所示,FLASH 翻转地址为 0x0040

\_ 69FA;翻转次数为 0x01,代表翻转 1 次;FLASH翻转位号为 0x57 的高三位,即 010b,代表第二片FLASH被打翻。状态信息可正常读取,表明定时器工作正常。

```

00000000h: 00 01 93 0A 00 50 00 00 17 0D C1 DD FB FF CE 70

00000010h: 01 00 00 05 03 84 89 72 A2 BC 04 00 00 00 00 01

2E 30 00 00 00 00 00 06 00

00000020h: 01

31 2E 31

00 00 00

00000030h:

00 00 00 00 00 00 00 00 00 00 00 00

00 00 00

00 00 00 00 00 00 00 00 00 00 00 00

00000040h:

00

00 55

00000050h ·

55

34 34

34

34 34 34 35 34 34 34 34 34

34

00000060h:

BD 93

7C

34 34 34 34

34 42

34

34

73

40

34

00000070h: 00 00 00 01 FF FF 09

41 00 14 00 01 E1

00000080h:

DE AC 15

4B

05 3F

FF FF 00 40 69 FA 09

00000090h:

00 01 2D 18

00 FF 01 57 01 10 01 10 00

000000a0h:

34

34 34

34

F4

34

34 34

000000b0h:

34 34

34

34 34 34 34 34

34 34

000000c0h:

34 34

34

34 34

34

34 34

34 00 02

34

34

000000d0h:

34

34 34 34

34 34 34

34 34 34 34 34 34

34

000000e0h:

34

34 AA AA FF 00 01 01 00 01 02 03 04

05 06 07

000000f0h: 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 14 15 16 17

```

图 10 FLASH 异常状态信息

当试验量级达到  $40\sim50$  k 之间时,定时器加电后 FPGA 加载失败,无任何状态信息上报。多次断电后再 次加电启动,现象一致,表明三片 FLASH 至少有 2 片 失效,定时器工作异常。

试验表明,采用3片FLASH三取二配置SRAM型FPGA的方式,可实现定时器一定空间辐照量级下的稳定运行。

2)模拟单粒子翻转效应:因单粒子翻转辐照试验仅针对芯片本身,无法完全对定时器整体试验,故采用故障注入的方式模拟定时器发生单粒子翻转,观察定时参数异常情况下定时输出情况。当定时参数正常时,定时时序满足定时器的预期,均按照要求产生脉冲信号;人为设置异常定时参数输入后,定时参数异常保护机制将该定时参数默认为缺省值,同时设置对应的定时时序为默认电平,不对外输出脉冲,确保异常情况下不会对系统各单元造成误触发。

定时器抗总剂量效应试验和模拟单粒子翻转试验表明,该定时器软硬件抗辐照措施有效,可确保在一定的空间辐照环境下,定时器可产生可靠稳定的定时时序;在单粒子翻转效应影响下,定时时序异常保护措施有效,可避免对系统各单元造成损伤。

#### 4 结束语

本文介绍了一种高可靠抗辐照定时器设计方法。该定时器基于 FPGA 架构,采用程序存储区三取二、定时刷新、关键定时参数异常保护、软件三模冗余、定时脉宽保护等措施,实现在空间辐照环境中产生稳定、可靠的系统定时时序。经总剂量试验和模拟单粒子翻转试验验证,定时器软硬件抗辐照措施有效,满足卫星等大型系统对定时器高可靠抗辐照时序产生的要求。

#### 参考文献:

- [1] 楼良盛, 刘志铭, 张 昊, 等. 天绘二号卫星关键技术 [J]. 测绘学报, 2022, 51 (12): 2403-2416.

- [2] 董瑶海. 风云四号气象卫星及其应用展望 [J]. 上海航天, 2016, 33 (2): 1-8.

- [3] 郭 强,陈博洋,张 勇,等.风云二号卫星在轨辐射定标技术进展「J].气象科技进展,2013,6(1):6-12.

- [4] 孙允珠, 蒋光伟, 李云端, 等. "高分五号"卫星概况及应用前景展望[J]. 航天返回与遥感, 2018, 39 (3): 1-13.

- [5] 张庆君. 高分三号卫星总体设计与关键技术 [J]. 测绘学报, 2017, 46 (3): 269-277.

- [6] 柯小路,王继生,李 洋. 一种高精度定时器设计方法 [J]. 电子技术与软件工程,2020 (3): 82-83.

- [7] 车 俐,蒋留兵,钱志强. FPGA 在雷达定时器中的应用 [J]. 电子工程师,2005,31 (8):7-9.

- [8] 褚兆文. 基于 FPGA 的雷达时序控制器设计与实现 [D]. 成都: 电子科技大学, 2007.

- [9] 柯小路,杨东华,王继生,等.一种软件化雷达定时器设计方法[J].现代雷达,2020,42(3):45-48.

- [10] 周立栋,孙永卫,蒙志成.复杂太空环境对航天器的影响「JT.飞航导弹,2017(7):65-69.

- [11] 郑晓云,陶淑苹,冯汝鹏,等. SRAM型 FPGA 抗单粒子翻转技术研究 [J]. 电子测量技术,2015,38 (1):59-63.

- [12] 黄锦杰. 抗单粒子翻转 SRAM-base FPGA 测试系统的研究与设计 [D]. 上海: 复旦大学, 2011.

- [13] 邢克飞,杨 俊,王跃科,等. Xilinx SRAM 型 FPGA 抗辐射设计技术研究 [J]. 宇航学报,2007,28 (1): 123-130.

- [14] 朱光武,李保权. 空间环境对航天器的影响及其对策研究 [J]. 上海航天,2002,4 (1):1006-1630.

- [15] 黄 影,张春元,刘东. SRAM 型 FPGA 的抗 SEU 方 法研究 [J].中国空间科学技术,2007,4:57-65.

- [16] 冯 兴,王大鸣,张彦奎,等. 基于 SRAM 型 FPGA 的 SEU 敏感性研究 [J]. 嵌入式技术,2016,42 (5):53-56.

- [17] 沈自才. 空间辐射环境工程 [M]. 北京: 中国宇航出版 社, 2013.

- [18] GJB / Z 24-1991 地球辐射带 [S].

- [19] 沈自才, 闫德葵. 空间辐射环境工程的现状及发展趋势 [J]. 航天器环境工程, 2014, 31 (3): 229-240.

- [20] 薛玉雄,曹 洲,杨世宇,等. 基于 Space Radiation 5.0 软件平台分析典型 GEO 空间辐射环境 [J]. 航天器环境工程,2007,24 (5):291-295.

- [21] 宋明龙,朱海元,章生平.卫星抗辐射加固技术 [J]. 上海航天,2001,18 (2):56-60.

- [22] 蔡震波. 新型航天器抗辐射加固技术的研究重点 [J]. 航天器环境工程, 2010, 27 (2): 173-176.