# 基于 RFSoC 的信号传播模拟器设计与实现

顾鹏程<sup>1,2</sup>

(1. 西南电子技术研究所, 成都 610036;

2. 复杂航空系统仿真全国重点实验室, 成都 610036)

**摘要:** 在实验室桌面条件下, 针对雷达、通信及侦察等射频传感器的半实物仿真需求, 对信号传播开展研究, 建模典型信号传播链路, 并为满足功能、性能、重量和体积指标, 提出了一种基于 RFSoC 芯片的信号传播模拟器, 并对时/空/频/能四维参数调制的实现方法进行分析。经过测试, 模拟器可实现  $20\text{ }\mu\text{s}\sim 1.2\text{ ms}$  范围的时域调制、支持四阵元干涉仪测向需求的空域调制、 $\pm 1\text{ MHz}$  范围内的频域调制、 $0\sim 63\text{ dB}$  范围内的能量域调制, 四维参数的调制准确度均大于 90%; 实测结果表明, 信号传播模拟器的研制能够为射频传感器半实物仿真的实施提供有力支撑。

**关键词:** 信号传播建模; 模拟器; RFSoC; 半实物仿真; 多维参数调制

## Design and Implementation of RFSoC-Based Signal Propagation Simulator

GU Pengcheng<sup>1,2</sup>

(1. Southwest Institute of Electronic Technology of China, Chengdu 610036, China;

2. National Key Laboratory of Complex Aviation System Simulation, Chengdu 610036, China)

**Abstract:** Under laboratory desktop conditions, this study investigates signal propagation to meet the hardware-in-the-loop simulation requirements of RF sensors such as radar, communication, and reconnaissance. Typical signal propagation links are modeled, and a signal propagation simulator based on an RFSoC chip is proposed to meet function, performance, weight, and volume requirements. The implementation method of four-dimensional parameter modulation (time, space, frequency, and energy) is analyzed. Testing shows that the simulator can achieve time-domain modulation in the range of  $20\text{ }\mu\text{s}$  to  $1.2\text{ ms}$ , spatial-domain modulation to support the direction finding requirements of a four-element interferometer, frequency-domain modulation in the range of  $\pm 1\text{ MHz}$ , and energy-domain modulation in the range of 0 to  $63\text{ dB}$ . The modulation accuracy of all four parameters is greater than 90%. Experimental results show that the development of the signal propagation simulator can provide strong support for the implementation of hardware-in-the-loop simulation of RF sensors.

**Keywords:** signal propagation modeling; simulator; RFSoC; hardware-in-the-loop simulation; multi-dimensional parameter modulation

## 0 引言

射频传感器研发过程中, 功能性能测试是必要的环节, 为了更高逼真地模拟射频传感器在实际场景中的工作状态, 需要使用模拟器搭建环境, 并模拟信号在实际空间中的传播情况。信号传播模拟在许多场景下均有需求, 通信设备测试与优化方面, 信号传播模拟器可模拟多径衰落、多普勒频移、时延扩展等复杂信道特性, 以协助验证基站、终端设备的抗干扰能力及协议性能, 在本领域内, 关注重点集中于多径衰落的模拟。在物联网和自动驾驶领域, 模拟器则被用于模拟高密度设备接入、车载通信的多普勒效应及遮挡场景, 主要侧重复杂场景

的信号变化模拟。无人机毫米波通信的信道建模需要依赖模拟器实现三维传播特性分析, 如机身姿态抖动对信号的影响<sup>[1]</sup>。卫星通信与深空探测方面, 针对卫星通信的长时延和大频移特性, 一批专用模拟器得以开发用于支持卫星导航三维信道建模<sup>[2-3]</sup>, 可精准模拟低轨卫星的动态链路衰减及对流层闪烁效应, 应用于卫星载荷的实验室验证, 并显著降低外场测试成本。在军事雷达及通信中, 雷达在复杂电磁环境下的功能性能, 以及通信设备的抗干扰测试, 亦需要信号传播模拟器的身影。

概括而言, 信号传播模拟器主要包含雷达回波模拟以及通信信道模拟两大类, 其功能及技术体制细节不尽相同。无论是雷达回波模拟器还是通信信道模拟器, 均

收稿日期:2025-06-19; 修回日期:2025-07-17。

作者简介:顾鹏程(1994-),男,硕士,工程师。

引用格式:顾鹏程. 基于 RFSoC 的信号传播模拟器设计与实现[J]. 计算机测量与控制,2025,33(12):278-285.

有商用货架产品大量面世。Keysight 公司的 Propsim F64<sup>[4]</sup>、Spirent 公司的 Vertex<sup>[5]</sup>、创远信科的 Pathrot X80 以及坤恒顺维的 KSW-WNS02 四款信道模拟器主要针对通信领域，为通信系统研发和测试提供了强大的工具，促进了 5G 和相关技术的发展和应用。但商用仪器频率范围及带宽有限，功能通常无法覆盖时空频能多域，控制接口较为固定，难以灵活嵌入自研测试验证系统中。2024 年，文献 [6] 基于 USRP 及 LabView 提出基于智能射线追踪（RT, ray trace）的信道计算与半实物仿真方法。将高精度 RT 仿真和超分辨率（SR, super-resolution）加速算法融合，解决了基于电子地图的 RT 信道建模精度、效率和算力成本无法兼顾的难题。该方案主要优势是侧重于信道建模而非硬件，同时 USRP 更适用于学术研究背景而非工业应用，使用场景存在局限。无独有偶，2017 年文献 [7] 描述了一种名为斗兽场（Colosseum）场景模拟器，其基于 USRP 搭建了  $256 \times 256$  共 65 536 个通道的高逼真射频场景模拟器，是当时世界上规模最大的室内信号传播模拟器。文献 [8] 在 2020 年采用两片 Virtex-7 690T FPGA 芯片，通过多通道并行处理技术实现 16 通道同步模拟，支持 100 MHz 带宽的瑞利/莱斯衰落生成，时延分辨率达 0.1 ns。其优势在于通过流水线设计将处理速度提升至传统 DSP 方案的 3 倍，适用于 5G Massive MIMO 系统测试。文献 [9] 于 2025 年基于国微 FPGA 芯片完成了回波模拟器采集组件的设计，在数据采集的同时，开发了适应多种速率的基于 UDP 协议的数据接口，探索了 FPGA 国产化的方案实现路径。纯 FPGA 类技术方案普遍长于处理速度，而如带宽等部分性能指标、设备相关控制需于 FPGA 外部实现，且由于 FPGA 与 ADC/DAC 的接口需普遍基于 JESD204B 开发，因此纯 FPGA 方案开发有一定难度。进一步地，文献 [10–11] 提出了基于 CPU+FPGA 的临空信道模拟器设计方案，整合大气吸收、降雨衰减与阴影衰落，支持 Rayleigh/Rician/Nakagami 等 7 种衰落模型的动态切换。通过有限马尔可夫链实现天气状态迁移，参数更新频率达 1 kHz，可模拟飞行器跨气候区的连续信道变化。然而 CPU 与 FPGA 相分离的方案通常通过 PCIE 协议进行板间通信，系统稳健性存在风险。近年来，以 ZYNQ+ADC/DAC 为核心芯片的方案也逐渐成为主流<sup>[12]</sup>，如文献 [13] 基于 ZYNQ 平台设计实现了可支持 75 MHz~6 GHz 频率范围，以及 200 MHz 带宽的两输入两输出信道模拟。其使用平台相较路辉方案提高了 FPGA 与 ARM 两大主要处理器的集成度，便于开发调试。相应地，文献 [14] 设计的天气雷达回波模拟器也采用这种方案。近年来，纯 FPGA 以及 ARM+FPGA 两种体制的国产化方案日趋完善与成熟。此外，还有围绕集成 FPGA 与 ADC/DAC 芯片开发的方案，如文献

[15] 基于安路 EG4S20BG256 实现的多通道模拟信号采集显示装置，其解决了 FPGA 与 ADC/DAC 连接开发的问题，但受限于芯片性能，大规模工业化应用仍存在性能不足的问题。

近年来，随着 Xilinx 于 2018 年提出集成 FPGA\ARM 以及 AD 器件的片上射频系统（RFSOC, radio frequency system on chip）芯片，基于 RFSOC 的方案也逐渐增多<sup>[16–17]</sup>，相较传统的 FPGA+AD 器件架构，RFSOC 相较成本的较小幅度提升，有效降低了射频信号链复杂性，简化了系统设计复杂性并有助于减少延迟，同时最大化提高输入/输出通道密度，增强了异构处理能力，在系统能效、外形尺寸缩减、设计周期缩短和设计灵活性方面具有显著优势。

本文首先对信号传播链路传播进行建模，随后设计并实现了基于 RFSOC 的信号传播模拟器，并从时空频能四维参数进行性能指标测试。该模拟器能有效模拟信号传输后接收端响应，可用作射频传感器半实物仿真系统的测试验证设备。

## 1 信号传播建模

由于本模拟器设计用于模拟无线信号在长距离传播的情况，故主要模拟大尺度衰落。大尺度衰落产生的主要原因是发射机和接收机之间传播路径上的山脉、植物、地理条件建筑物等对信号的阻挡，是一种变化相对慢的衰落。

理论上，信号可认为是在自由空间中传播，自由空间指满足电波传播各向同性、电导率为零以及均匀无损耗的无限大空间等条件的理想空间。在自由空间中，电磁波的传播不会受到绕射和散射等物理现象的影响，并且其传播速度是光速  $c$ ，传播过程中会因为距离增大的能量损耗而形成衰落。

假设发射端和接收端之间的距离表示为  $d$ ，并且使用各向异性的天线，电磁波信号在自由空间中传输到接收端，那么接收天线收到的信号功率  $P_r$  则与发射功率  $P_t$  之间关系服从 Friis 公式，即：

$$\frac{P_r}{P_t} = \frac{G_t G_r \lambda^2}{(4\pi)^2 d^2 L} \quad (1)$$

其中： $P_t$  为发射功率， $G_t$  为发射天线增益， $G_r$  为接收天线增益， $L$  为系统损耗系数，具体包括各种器件损耗， $\lambda$  则为信号波长。

在自由空间中，路径衰减由于不存在多径衰落以及阴影衰落的影响，可等效为发射功率和接收功率之差，即：

$$PL(\text{dB}) = -10 \lg \left( \frac{P_r}{P_t} \right) = -10 \lg \left[ \frac{G_t G_r \lambda^2}{(4\pi)^2 d^2 L} \right] \quad (2)$$

若进一步不考虑天线增益，并将  $\lambda = \frac{c}{f}$  代入上式，

可得：

$$PL(\text{dB}) = -10 \lg \left[ \frac{\left( \frac{c}{f} \right)^2}{\left( 4\pi \right)^2 d^2} \right] = -10 \lg \left[ \frac{c^2}{\left( 4\pi \right)^2} \right] + 20 \lg(d) + 20 \lg(f) \quad (3)$$

当  $f$  的单位取 MHz,  $d$  的单位取 km 时, 可化简得:

$$PL(\text{dB}) = 32.45 + 20 \lg(d) + 20 \lg(f) \quad (4)$$

除功率衰减外, 信号经传播后, 还会由于运动、距离存在频率、相位、时间偏差。可将接收信号建模如下:

$$y(t) = h e^{j\varphi} e^{j2\pi f t} s(t - \tau) + \omega(t) \quad (5)$$

其中:  $h$  为衰减系数,  $\varphi$  为相位偏差,  $\Delta f$  为频率偏差,  $\tau$  为时间偏差, 而  $\omega(t)$  是高斯白噪声。

综上, 信号传播需对信号的时间、空间(相位)、频率、能量四维参数进行调制处理。

## 2 总体设计

### 2.1 方案概述

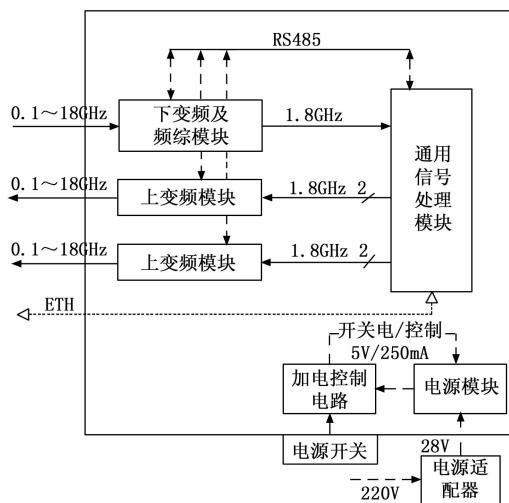

为覆盖 0.1~18 GHz 频段, 同时保证较宽处理带宽, 设计经典“下变频—中频处理—上变频”架构作为信号传播模拟器架构。如图 1 所示。

图 1 系统逻辑视图

信号传播模拟器软硬件均采用模块化设计, 其中硬件可具体划分为下变频及频综模块、上变频模块、通用信号处理模块以及电源模块。通用信号处理模块作为核心模块, 通过以太网接收来自上位机的信道调制参数信息, 经 ARM 解析与转译后下发至 FPGA, 完成中频信号处理, 同时 ARM 配置射频控制参数到下变频及频综模块以及上变频模块。

模块核心采用 RFSoC 芯片 XCZU47DR, XCZU47DR 资源较为丰富, 主要包括两路网口、4 路 RS485 接口、两路 RS232 接口、LVDS 收发接口、EMMC、DDR、复位电路、8 路 ADC、8 路 DAC 等电路。信号收发方

面, XCZU47DR 内部包含 8 个 14 bitADC, 最高采样率为 5 Gsps, 包含 8 个 14 bitDAC, 最高采样率为 9.85 Gsps。

### 2.2 模拟器设计指标

本信号传播模拟器主要对时空频能四维参数进行调制模拟, 主要预期指标如下:

- 1) 工作信号频率范围: 0.1~18 GHz;

- 2) 接收通道数: 1 路, 发射通道数: 4 路;

- 3) 模拟目标相对运动速度范围:  $\pm 2040 \text{ m/s}$  (相对 6 马赫);

- 4) 模拟目标距离范围: 单程 1~400 km, 双程 1~200 km;

- 5) 时域调制: 范围为  $20 \mu\text{s} \sim 1.2 \text{ ms}$ , 步进为 3.33 ns;

- 6) 空域调制: 模拟角度能适配四阵元干涉仪  $\pm 60^\circ$  测向需求;

- 7) 频域调制: 范围  $\pm 1 \text{ MHz}$ , 步进: 10 Hz;

- 8) 能量域调制: 范围 0~63 dB, 步进: 0.5 dB。

## 3 硬件设计

由上节可知, 系统硬件包含下变频及频综模块、上变频模块、通用信号处理模块以及电源模块。模块间通过背板 RS485 总线实现互联互通, 如图 1 所示。

### 3.1 通用信号处理模块设计

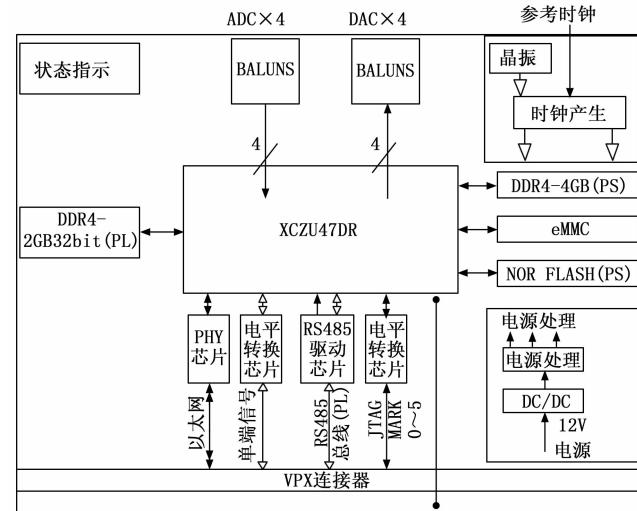

通用信号处理模块主要实现变频后中频信号的收发处理工作。综合考虑设备小型化研发需要以及后续扩展性, 模块采用 3U VPX 标准结构, 模块原理如图 2 所示。

图 2 通用信号处理模块原理框图

中频信号经过抗混叠滤波、信号增益调整后, 由 Balun 将单端信号转换为差分形式输入 RFSoC 的 ADC 内核进行采集; 由 RFSoC 的 PL 端引出 PCIe、GTX、DDR 等接口用于系统及外设互联; PS 端外接 EMMC、DDR4、Flash 等电路用于 ARM 处理器的程序运行。

1) Balun: RFSOC 输入输出阻抗为  $100\ \Omega$ , 前端信号输入阻抗为  $50\ \Omega$ , 选择  $1:2$  阻抗 Balun, 由于通用信号处理模块设计输入信号频率为  $1.8\text{ GHz} \pm 500\text{ MHz}$ , 选用能覆盖该频段的 Balun。ADC 和 DAC 保留所有端口, 根据收发处理需求, 通过射频线缆选通 8 路连到 VPX 连接器中。

2) DDR: 模块设计了 2 组 DDR4 接口, ARM 接一组, FPGA 接一组。

3) EMMC: 模块设计 8 GB EMMC 用于存储 Linux 系统相关文件。

4) RS485: 共设计 4 路 RS485 接口, 3 路 RS485 总线接 ARM, 1 路 RS485 离散线接 FPGA, 实际最大传输速率为 10 Mbps。

5) PCIE: 根据使用需求, 模块设计两组 PCIE 总线, 分别为 ARM 的 PCIE2.0X4 和 FPGA 的 PCIE3.0X8。

6) LVDS: 根据使用需求, 模块设计 5 路 LVDS 输入和 5 路 LVDS 输出, 均接 FPGA。

7) 用于调试的 JTAG 电路, 设计由 RFSOC 的 JTAG 通过电平转换芯片 SN74AVC4T245 做隔离后引出到调试连接器。

8) 时钟: 由于 RFSOC 的多路 ADC 采样通道需要严格同步, 对时钟要求较高。选定 HMC7044, 其能选择参考并生成超低相位噪声的频率。

9) 背板: 12 V 电源由 VPX 背板 P0 口引入, 经过电压转换处理后为板上各芯片提供电源信号; P1 提供与 RFSOC 相连的 8 根单端 IO、6 对差分 422 输出信号、3 对差分 422 输入信号, 3 对 LVDS 输入, 5 对 LVDS 输出、1 个 RS422 接口、1 个千兆网口以及 1 个 UART。P3 布置为参考时钟输入以及射频信号输入

输出。

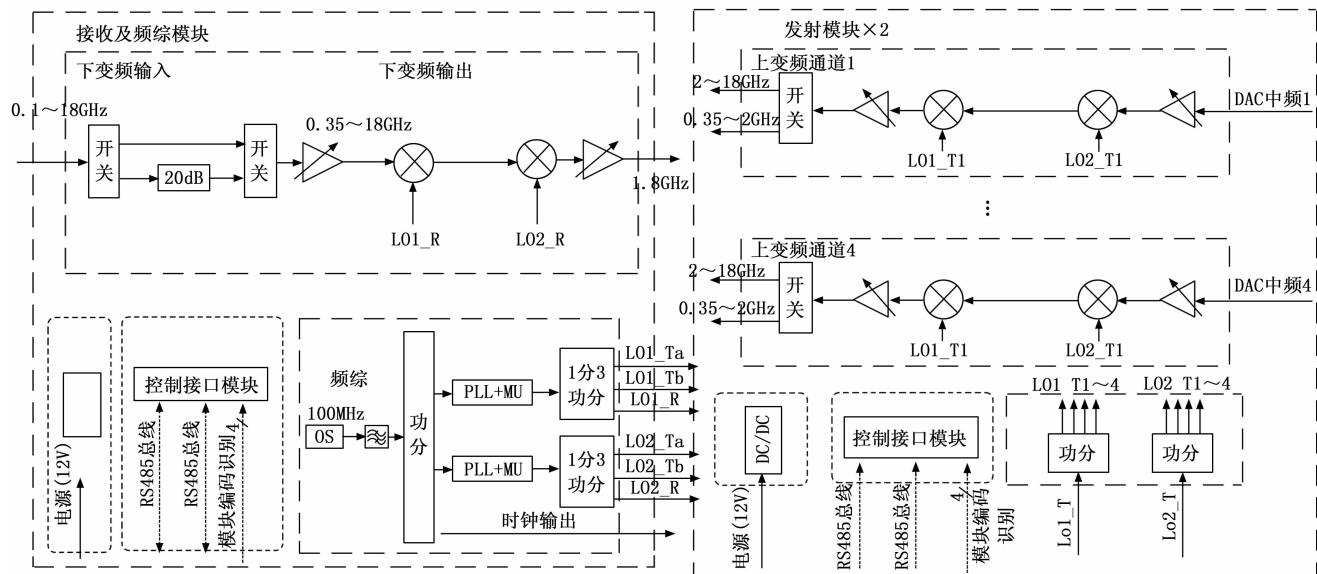

### 3.2 射频模块设计

为实现“射频——中频”及“中频——射频”变换。综合考虑, 设计射频模块包括一个接收及频综模块以及两个发射模块, 如图 3 所示。

接收及频综模块中主要实现 1 路  $0.1\sim18\text{ GHz}$  射频信号到中频频率  $1.8\text{ GHz}$  的转换, 同时产生本振供自身及其他模块使用。接收变频信道单元包括滤波、放大、衰减、频率预选、混频等。采用两次变频方案, 一本振及二本振均使用  $18\text{ GHz}$  以上频率。本振采用锁相环+2 倍频器方式实现, 频率切换时间小于  $100\ \mu\text{s}$ 。

发射模块共两块, 每块发射模块实现两路中频信号从  $1.8\text{ GHz}$  变频到  $0.1\sim18\text{ GHz}$  射频信号的转换发射模块信道单元包括滤波、放大、衰减、频率选频、混频等。与接收模块相似, 发射模块也采用两次变频。

## 4 软件设计

### 4.1 软件体系设计

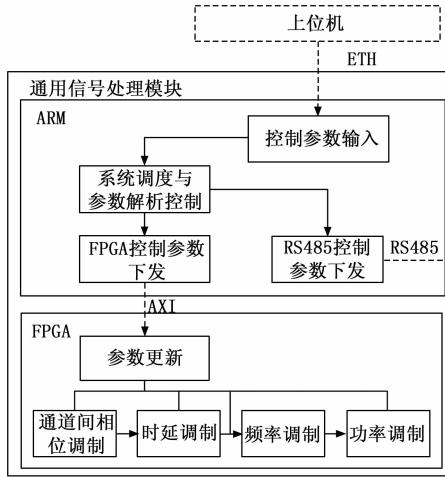

信号传播模拟器的主要模拟功能由通用信号处理模块上驻留的 FPGA 数字信号处理软件和 ARM 调度处理软件共同完成。信号传播模拟器软件体系结构层次如图 4 所示。

信号传播流程如下:

1) ARM 初始化设备并完成自检;

2) ARM 周期接收并解析上位机通过以太网下发的信号传播调制控制参数。

3) ARM 将控制参数解译成功率、角度、多普勒、时延调制所需参数。

4) ARM 通过 AXI 总线配置 FPGA 工作参数至 FPGA, 通过串口配置射频控制参数至上下变频模块。

图 3 射频模块设计

图 4 通用信号处理模块软件结构

5) 上下变频模块、FPGA 分别响应相应的工作参数并进行信号处理。

对于设计需求中的时、空、频、能四维参数模拟指标, 上位机下发经仿真计算的四维调制参数, ARM 主要实现模拟调制参数解析与转发, FPGA 实现具体信号的模拟调制处理。

## 4.2 ARM 软件设计

ARM 软件是通用信号处理模块的控制中心, 运行于 Linux 系统中。ARM 软件由通用信号处理模块上电启动后, 通过运行脚本调用在后台运行。

根据需要实现的功能和任务, ARM 软件可以划分为 4 个主要的软件模块。

1) 初始化模块: 完成上电后 ARM 工作参数初始化、FPGA 工作参数初始化。其中 ARM 工作参数初始化包括: 信号量初始化、线程初始化、以太网初始化等配置。FPGA 工作参数初始化包括: ADC/DAC 通道选通、时频相位计算参数等配置。

2) 网络消息接收模块: 主要完成以太网接收及消息入队。

由设计需求可知, 来自网络的消息处理周期需满足不低于 20 ms, 故网络消息接收模块需尽可能缩短消息接收处理时间开销, 因此消息接收部分仅对消息帧的帧头帧尾、帧长、帧 ID 进行校验, 若均匹配通过, 则后传继续处理。同时由于调制则将其复制并压入队列等待调制参数解析。入队和出队使用线程锁保证处理安全。消息接收部分从 socket 端口接收至完成入队, 实测整个处理时间小于 75  $\mu$ s, 满足要求。

3) 调制参数解析模块: 本模块基于队列, 主要完成控制指令参数解析、调制参数解算的功能。

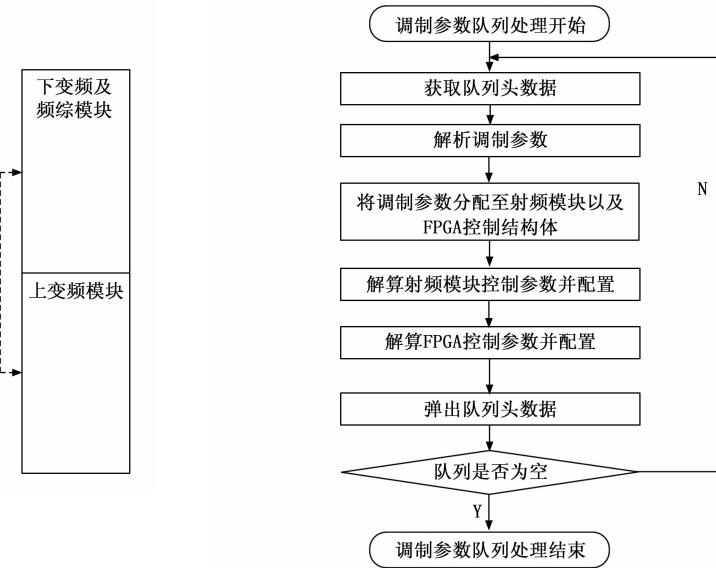

如图 5 所示, 调制参数解析模块处理对象为调制参数队列, 首先获取队列头的数据, 所需解析的调制参数具体包括: 信号频率、调制与开关使能标志、模拟角

图 5 调制参数解析模块工作流程

度、模拟距离、模拟速度等。在接收到参数后, 根据参数类型, 分配至射频模块及 FPGA 控制的结构体, 并分别进行解算与配置。完成处理后, 弹出队列头数据, 随后判断队列是否为空。若不为空, 则继续获取队列头数据并处理, 若为空则处理结束。

两者需要解算的调制参数包括以下 3 类:

(1) 模拟距离参数。上位机根据接收的模拟距离数值与信号频率, 通过电波传播模型解算对应的衰减值及时延值, 直接下发至 ARM 软件。衰减值根据“射频衰减优先”以及“精细衰减由 FPGA 实现”两大原则, 将具体数值合理分配至 FPGA 和射频模块, 同时还需根据信号频率计算合理的本振频率并配置至射频模块。时延参数亦分解为大时延及小时延, 下发给 FPGA。

(2) 模拟速度参数。上位机根据接收的模拟速度数值与信号频率, 通过电波传播模型解算对应的多普勒频移值, 直接下发至 ARM 软件。ARM 软件根据 FPGA 工作参数换算得到频移配置参数, 下发给 FPGA。

(3) 模拟角度参数。上位机根据接收的模拟角度数值与信号频率, 结合配置的多通道基线数值, 通过电波传播模型解算不同通道相对 1 通道的相位差, 直接下发至 ARM 软件。ARM 软件换算得到相位配置参数, 后续下发给 FPGA。

在本模块设计实现时, 对每种参数的计算和配置均进行细致代码实现及优化, 尽可能减少时间开销大的内存复制等操作。经过对重要功能函数进行时间测量, 实测结果如表 1 所示。

由上可知, 调制参数解析模块对单个调制参数解析的处理运行耗时不足 1.8 ms, 满足指标要求。

4) 状态监测模块: 实现对温度监测、电源监测、

表 1 调制参数解析模块耗时

| 功能大类    | 功能模块    | 耗时 / $\mu\text{s}$ |

|---------|---------|--------------------|

| 参数接收与分配 | 功率分配    | 10                 |

|         | 射频分配与配置 | 29                 |

|         | FPGA 分配 | 25                 |

|         | 小计      | 63                 |

| 参数转换    | 多普勒部分   | 233                |

|         | 衰减部分    | 215                |

|         | 时延部分    | 289                |

|         | 相位部分    | 350                |

|         | 小计      | 1 260              |

| 总计      |         | 1 738              |

FPGA 工作参数、ARM 工作状态的监控。FPGA 工作参数包括版本信息、参数配置情况等；ARM 工作状态包括版本信息等。

### 4.3 FPGA 软件设计

FPGA 具体负责通用信号处理模块的数字域信号处理部分，根据需要实现的功能和任务，FPGA 可以划分为 3 个主要的软件模块。

#### 4.3.1 模块设计

1) ARM 参数收发模块，用于接收 ARM 下发的控制参数，同时能发送数据至 ARM。

2) ADDA 通用信号处理模块，具体包含相位调制运算模块、多普勒调制运算模块、时延调制运算模块以及功率调制运算模块，用于完成信号传播模拟，同时还配置了校准信号产生模块以及必要控制模块，增强设备功能。

3) 基础驱动模块，具体包含 ADDA 驱动、时钟模块等，支撑实现信号采集等基础功能。

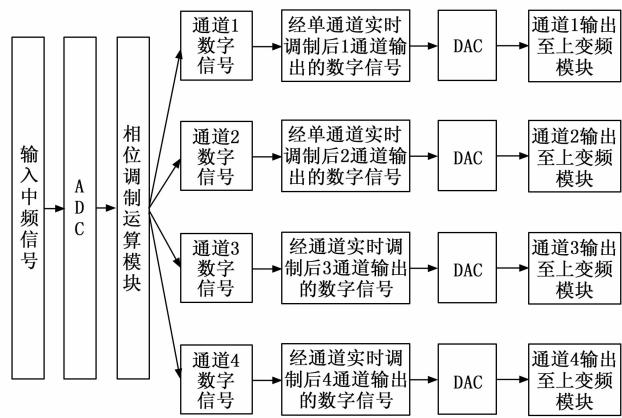

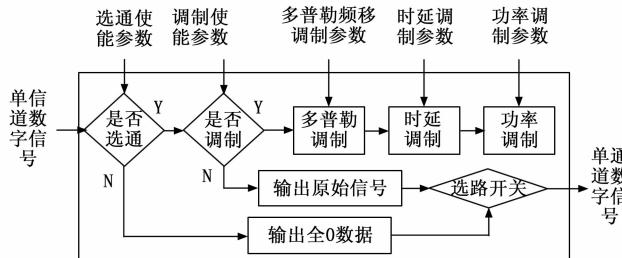

FPGA 内信号处理流程如图 6 所示。输入通用信号处理模块的中频信号经 ADC 采样后输出数字信号，进行相位调制运算后，产生 4 路数字信号，随后对每路信号进行单通道实时调制处理。单通道实时调制处理包含多普勒频移调制、时延调制、功率调制 3 个部分。

#### 4.3.2 调制算法实现设计

##### 1) 时域调制：

时延调制的本质是存储后再读出，根据设计需求，考虑采用两级不同速率的 BRAM 存储级联，实现步进达到 3.33 ns，同时最大时延不小于 1.2 ms 的时延调制。

由于 FPGA 工作频率为 300 MHz，一个时钟节拍即对应 3.33 ns，因此控制步进可满足要求。而相同 BRAM 深度，慢时钟能实现更大范围的时延，因此设计通过上下变频、低通滤波以及抽取插值实现多速率处理，将 300 MHz 时钟对应的信号通过下变频、滤波、抽取变至 37.5 MHz 时钟再进行延时，此时由于时钟节拍变长，利于进行大延时处理。完成大时延处理后，

(a) FPGA 处理流程图

(b) 单通道实时调制处理流程图

图 6 单通道数字信号处理流程图

再通过插值、滤波、上变频完成信号时钟域恢复。

根据设备资源情况，分配大时延部分 BRAM 深度不小于 130 000。小时延部分 BRAM 深度为 1 024，此时能模拟时延范围最大达到 3.5 ms，对应单程距离为 1 050 km，满足要求。

##### 2) 相位调制：

多通道的相位调制本质是对一路信号进行不同参数的复乘实现。

由于硬件设计实现过程中，无法完全消除由于链路不同带来的通道间相位差，因此在相位调制模块中，需同时实现相位校正以及相位调制两部分功能。

##### 3) 多普勒调制：

多普勒调制本质是对中频信号进行变频。使用一个 DDS 模块产生变频需要的数字载波数据，输入信号与 DDS 产生的载波数据进行复乘，即得到多普勒频偏调制后的中频数据。

由于相位调制及多普勒调制均存在复乘运算，而 FPGA 的整数复乘运算存在位数扩展的情况，不利于后续处理。故需要通过仿真确定适当的移位位数，完成复乘后进行右移除法缩小数值，同时尽可能减小处理过程中的功率损耗。

##### 4) 功率调制：

FPGA 的功率调制主要针对精细的调整，而具体功能通过对输入数据进行幅度加权系数复乘得到的。根据设计需求，FPGA 部分需能实现范围 35 dB 且步

进 0.5 dB 的功率调制精度, 由于 FPGA 仅支持整型数据运算, 故考虑先进行整数乘法放大后再通过左移除法, 实现小数乘法。

根据仿真, 当衰减 dB 值从 0.1 变化到 35 时, 所对应的幅度加权系数值由 0.988 6 变化到 0.017 78, 如图 7 所示。

|    | B           | 338 | 0.020417379 |

|----|-------------|-----|-------------|

| 1  | 0.988553095 | 339 | 0.020183664 |

| 2  | 0.977237221 | 340 | 0.019952623 |

| 3  | 0.966050879 | 341 | 0.019724227 |

| 4  | 0.954992586 | 342 | 0.019498446 |

| 5  | 0.944060876 | 343 | 0.019275249 |

| 6  | 0.933254301 | 344 | 0.019054607 |

| 7  | 0.922571427 | 345 | 0.018836491 |

| 8  | 0.912010839 | 346 | 0.018620871 |

| 9  | 0.901571138 | 347 | 0.01840772  |

| 10 | 0.891250938 | 348 | 0.018197009 |

| 11 | 0.881048873 | 349 | 0.017988709 |

| 12 | 0.87096359  | 350 | 0.017782794 |

图 7 衰减 dB 值放大 10 倍后, 衰减值与幅度加权系数的对应

由图 7 可知, 当扩大 10 倍后, 小数乘法运算需至少保留到小数点后第四位, 才能区分不同原始衰减值。

由图 8 可知, 至少需要放大至  $2^{12}$  倍后, 才可通过个位分辨出不同原始衰减值。

| A     | B           | C       | D | E        | F        | G        | H        | I        |

|-------|-------------|---------|---|----------|----------|----------|----------|----------|

| value | 小数          | 舍入后的值   |   | 右移10     | 右移11     | 右移12     | 右移13     | 右移14     |

| 344   | 0.019054607 | 0.01905 |   | 19.51192 | 39.02384 | 78.04767 | 156.0953 | 312.1907 |

| 345   | 0.018836491 | 0.01884 |   | 19.28857 | 38.57713 | 77.15427 | 154.3085 | 308.6171 |

| 346   | 0.018620871 | 0.01862 |   | 19.06777 | 38.13554 | 76.27109 | 152.5422 | 305.0844 |

| 347   | 0.01840772  | 0.01841 |   | 18.84951 | 37.69901 | 75.39802 | 150.796  | 301.5921 |

| 348   | 0.018197009 | 0.01820 |   | 18.63374 | 37.26747 | 74.53495 | 149.0699 | 298.1396 |

| 349   | 0.017988709 | 0.01799 |   | 18.42044 | 36.84068 | 73.68175 | 147.3635 | 294.727  |

| 350   | 0.017782794 | 0.01778 |   | 18.20958 | 36.41916 | 72.83832 | 145.6766 | 291.3533 |

图 8 加权系数在不同放大倍数作用下的对应值

故设计 FPGA 实现小数乘法算法如下:

ARM 获得衰减值 (dB) 后, 乘 10 得到  $a$ , 对  $a$  求

$\frac{1}{10^{0.005 * a}}$  的值后乘以  $2^{13}$ , 将乘积四舍五入得到转化因子  $b$ , 通过寄存器配置至 FPGA。FPGA 使用乘法器将  $b$  与 IQ 数据进行相乘, 随后将乘法器输出值右移 13 位, 所得值即为衰减后的幅度值, 完成小数乘法。

#### 4.3.3 小结

经过合理设计, FPGA 软件在完成功能指标要求的同时, 降低了开发与维护难度, 减小了硬件资源开销, 硬件资源使用情况如表 2 所示。

表 2 FPGA 硬件资源使用情况

| 资源名    | 使用量    | 全部量     | 使用比例/% |

|--------|--------|---------|--------|

| LUT    | 49 674 | 425 280 | 11.68  |

| LUTRAM | 7 909  | 213 600 | 3.70   |

| FF     | 62 673 | 850 560 | 7.37   |

| BRAM   | 688.5  | 1 080   | 63.75  |

| DSP    | 360    | 4 272   | 8.43   |

| IO     | 12     | 152     | 7.89   |

| BUFG   | 9      | 696     | 1.29   |

| MMC    | 1      | 8       | 12.5   |

## 5 测试结果

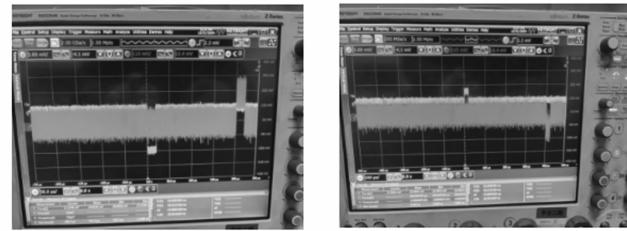

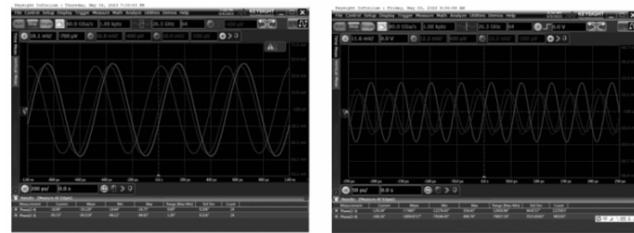

对信号传播模拟器进行时延、相位、频率、功率四维参数的调制性能进行测试。其中时延及相位使用多通道示波器进行测量, 频率及功率使用频谱分析仪进行测试, 如图 9 所示。

图 9 时延调制测试

## 5.1 时延调制测试结果

经测试, 时延调制范围能覆盖  $20 \mu s \sim 1.2 ms$ , 满足要求。

## 5.2 相位调制测试结果

如图 10 所示, 对  $0.1 \sim 18 GHz$ , 取若干典型频率, 校准后配置不同基线与  $0^{\circ}$ 、 $15^{\circ}$ 、 $30^{\circ}$ 、 $45^{\circ}$  入射角, 计算得到的相位差与理论相位差的误差与准确度。经测试, 调制误差平均为  $2.8^{\circ}$ , 准确度为 96.97%。

图 10 相位调制测试

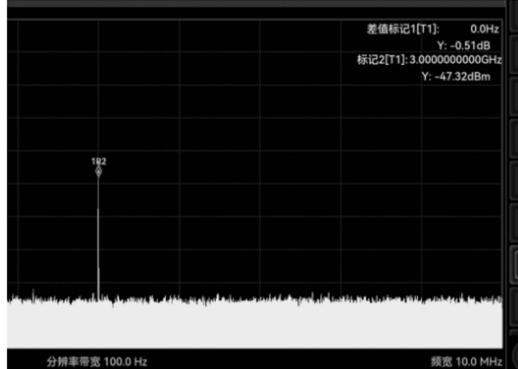

## 5.3 频率调制测试结果

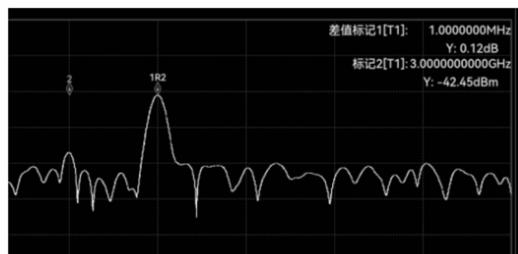

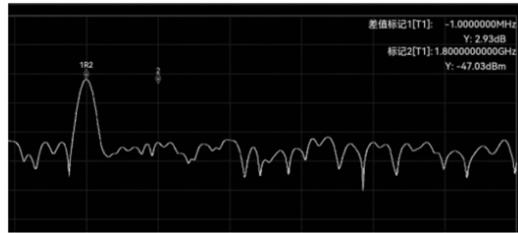

如图 11 所示, 对  $0.1 \sim 18 GHz$ , 取若干典型频率, 分别以 1% 和 2% 的频率调制值, 计算其误差与准确度。

经测试, 调制误差平均为  $0.29 kHz$ , 准确度为 99.6%。

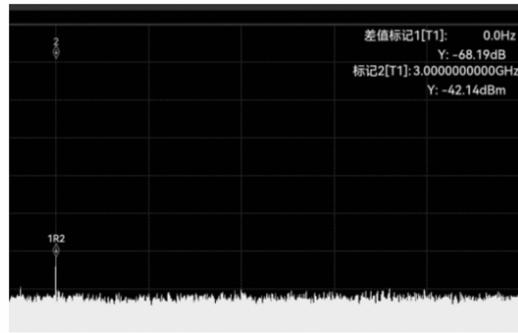

## 5.4 功率调制测试结果

如图 12 所示, 对  $0.1 \sim 18 GHz$ , 取若干典型频率, 分别配置 2、8、14、20 dB 衰减值, 计算其误差与准确度。

经测试, 功率调制误差平均为  $0.22 dB$ , 准确度为 94.92%。

## 6 结束语

基于 RFSoC 的信号传播模拟器与传统方案相比, 由于其核心芯片 RFSoC 同时集成 ADDA 组件、ARM 通用处理器、FPGA 逻辑处理单元, 因此在设备小型化

(a) 3 GHz, 10 Hz 调制

(b) 3 GHz, -1 MHz 调制

图 11 频率调制测试

(a) 3 GHz, 68 dB衰减

(b) 3 GHz, 0.5 dB衰减

图 12 功率调制测试

方面具有得天独厚的优势。进一步地, 同时相比其他架构, 本方案在开发、调试、控制方面均具备更高效率、更灵活配置、更强大扩展性的优势。而设备对信号频率、功率、相位、时间四维参数实现精度较高、范围较大的调制控制, 能满足其在室内环境下对信号传播进行高逼真度模拟的功能, 已在多个项目中投入使用。后续作者还将继续深入研究信号传播模拟器中实现多径的方法, 并对高精度校准进行研究, 从而丰富设备功能, 提

高设备的性能指标。

### 参考文献:

- [1] 朱秋明, 倪浩然, 华博宇, 等. 无人机毫米波信道测量与建模研究综述 [J]. 移动通信, 2022, 46 (12): 2–11.

- [2] 李蓬蓬. 导航卫星信道模拟器关键技术研究 [D]. 长沙: 国防科学技术大学, 2014.

- [3] 岳宇航. 卫星信道模拟器延时技术研究 [D]. 长沙: 国防科学技术大学, 2015.

- [4] KEYSIGHT. PROPSIM F64 radio channel emulator [EB/OL]. (2023-03-21) [2023-09-30]. <https://www.keysight.com/cn/zh/assets/7018-06665/data-sheets/59924078.pdf>.

- [5] SPIRENT. Vertex channel emulator [EB/OL]. (2021-11-21) [2023-09-30]. [https://www.spirent.com/assets/uspirent\\_vertex\\_channel\\_emulator\\_datasheet](https://www.spirent.com/assets/uspirent_vertex_channel_emulator_datasheet).

- [6] 刘煜鑫, 何丹萍, 单馨漪, 等. 基于智能射线追踪的信道计算与半实物仿真 [J]. 电波科学学报, 2024, 39 (6): 1112–1119.

- [7] BONATI L, JOHARI P, POLESE M, et al. Colosseum: large-scale wireless experimentation through hardware-in-the-loop network emulation [C] //Proceedings of IEEE DySPAN, Virtual Conference, 2021.

- [8] 廖海华. 基于 FPGA 的数字无线信道模拟器研究与设计 [D]. 深圳: 深圳大学, 2020.

- [9] 李森, 王建明, 唐吉林. 基于 FPGA 与 PCIe 的回波模拟器采集组件设计 [J]. 空天预警研究学报, 2025, 39 (1): 67–73.

- [10] 路辉, 刘雪妍. 基于 CPU+FPGA 的实时临空信道模拟器设计 [J]. 计算机测量与控制, 2023, 31 (11): 286–292.

- [11] 路辉, 董昕玉. 基于 CPU+FPGA 的临近空间信道模拟器设计 [J]. 计算机测量与控制, 2021, 29 (9): 161–169.

- [12] 张恒冲. 基于 ZynqMPSoC 的高超声速飞行器综合信道模拟器设计 [D]. 西安: 西安电子科技大学, 2023.

- [13] 严康宁. 无线信道模拟方法研究与设备研制 [D]. 南京: 东南大学, 2022.

- [14] 许洋, 李学华, 王俊, 等. 基于 AD9361 的天气雷达回波模拟与硬件系统 [J]. 成都信息工程大学学报, 2024, 39 (3): 283–290.

- [15] 汪兴海, 孟翔麒, 秦刚, 等. 多通道模拟信号采集显示装置设计 [J]. 计算机与数字工程, 2024, 52 (2): 616–621.

- [16] 贾渺一, 吴柯锐. 基于 Zynq RFSOC 的信号收发系统设计 [J]. 舰船电子工程, 2024, 44 (12): 73–77.

- [17] 师浪, 张瑞安, 张宾. 基于 RFSOC 的小型化侦察干扰系统实现 [J]. 电子设计工程, 2024, 32 (19): 135–139.