文章编号:1671-4598(2024)01-0304-08 DOI:10.16526/j.cnki.11-4762/tp.2024.01.043 中图分类号:TP27; TP274 文献标识码:A

# Virtex-5 系列 SRAM 型 FPGA 单粒子效应 重离子辐照试验技术研究

赖晚玲 $^{1,2}$ 、郭阳明 $^{1}$ 、巨 艇 $^{2}$ 、朱 启 $^{2}$ 、贾 亮 $^{2}$

- (1. 西北工业大学 计算机学院, 西安 710072;

- 2. 中国空间技术研究院 西安分院, 西安 710000)

摘要: 针对 SRAM 型 FPGA 在空间辐射环境下易发生单粒子效应,影响星载设备正常工作甚至导致功能中断的问题,开展了 SRAM 型 FPGA 单粒子效应地面辐照试验方法研究,提出了配置存储器 (CRAM) 和块存储器 (BRAM) 的单粒子翻转效应测试方法,并以 Xilinx 公司工业级 Virtex-5 系列 SRAM 型 FPGA 为测试对象,设计了单粒子效应测试系统,开展了重离子辐照试验,获取了器件的单粒子闩锁试验数据和 CRAM、BRAM 以及典型用户电路三模冗余前后的单粒子翻转试验数据;最后利用空间环境模拟软件进行了在轨翻转率分析,基于 CREME96 模型计算得到 XC5 VFX130 T 器件配置存储器 GEO 轨道的单粒子翻转概率为 6.41×10<sup>-7</sup>次/比特・天。

关键词: SRAM 型 FPGA; 单粒子效应; 单粒子翻转; 单粒子闩锁; 重离子辐照试验

# Research on Heavy Ion Irradiation Test Method for Single Event Effects of Virtex-5 SRAM FPGA

LAI Xiaoling<sup>1,2</sup>, GUO Yangming<sup>1</sup>, JU Ting<sup>2</sup>, ZHU Qi<sup>2</sup>, JIA Liang<sup>2</sup>

(1. School of Computer Science, Northwestern Polytechnical University, Xi'an 710072, China;

2. Xi'an Institute of Space Radio Technology, Xi'an 710000, China)

Abstract: To address the problem that SRAM FPGA is prone to single event effect (SEE) in space radiation environment, which may affect the normal operation of space borne electronic equipment or even lead to functional interruptions, a research on the ground irradiation test method of SRAM FPGA's SEE was conducted. The single event upset (SEU) test method of CRAM and BRAM was proposed. The test system was designed using the Xilinx Virtex-5 series industrial-grade SRAM FPGA as the test object, and the heavy ion irradiation test was carried out. The device's single event latch-up (SEL) test data and the SEU test data of CRAM, BRAM, and the typical user circuits before and after TMR were obtained. Finally, the SEU rate was analyzed using space environment simulation software. Based on the CREME96 model, the SEU probability of CRAM of XC5VFX130T in GEO orbit was calculated to be 6.41×10<sup>-7</sup> times/bit • day.

Keywords: SRAM FPGA; single event effects; single event upset; single event latch-up; heavy ion irradiation test

#### 0 引言

静态随机存储器(SRAM, static random access memory)型现场可编程逻辑门阵列(FPGA, field programmable gate array)是一种可以重复编程的 FPGA, 电路功能由存储在器件内部配置存储区的配置文件确定,用户可以通过配置接口进行在线调试或者远程加载。随着微电子技术的不断进步,SRAM型 FPGA 已经发展成为具有丰富的可编程逻辑资源,支持高速应用的大规模可编程器件。由于SRAM型 FPGA 具有高性能、可重构的优点,已经广泛应

用于宇航领域,成为星载设备的核心处理器件<sup>[1-3]</sup>。但是 SRAM型 FPGA 具有大量配置存储单元,在空间环境下受到高能粒子轰击可能发生单粒子效应从而对电路功能产生影响,因此空间应用时必须进行单粒子效应敏感性评估和 防护设计<sup>[1-5]</sup>。

Xilinx 公司的 SRAM 型 FPGA 器件功能强大、性能优异。根据性能、资源和规模的不同,该公司的 SRAM 型 FPGA 器件可分为 Spartan、Artix、Kintex 和 Virtex 系列等。其中, Virtex 系列是 Xilinx 公司的高端器件,具有逻

收稿日期:2023-06-07; 修回日期:2023-07-18。

基金项目:飞行器控制一体化技术国防科技重点实验室基金(6142219200205)。

作者简介:赖晓玲(1982-),女,硕士,高级工程师。

引用格式:赖晓玲,郭阳明,巨 艇,等. Virtex-5 系列 SRAM 型 FPGA 单粒子效应重离子辐照试验技术研究[J]. 计算机测量与控制, 2024,32(1):304-311.

辑资源丰富、高带宽、高速度和大规模集成的特点,适用 于高端通信、数据中心、嵌入式视觉、高性能计算和控制 系统等领域,也越来越多的应用在航空航天中<sup>[6]</sup>。

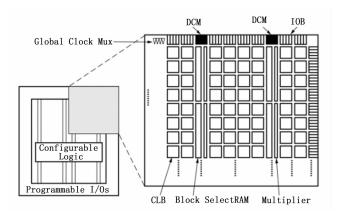

SRAM型 FPGA 可以看作由配置存储器和用户可编程逻辑构成的两层架构<sup>[7]</sup>。用户可编程逻辑包括可编程块(CLB, configuration logic block)、IO块(IOB, IO Block)、块存储器(BRAM, block RAM)、数字时钟管理模块(DCM, digital clock manager)、DSP48、其他资源(如处理器核、PCIe、高速接口等)。用户可编程逻辑的具体功能与连接关系由配置存储器(CRAM, configuration RAM)决定。SRAM型 FPGA 两层架构示意图如图 1 所示。

图 1 SRAM型 FPGA 两层架构示意图[7]

根据国内外试验研究[8-9], Xilinx 公司的 SRAM 型 FP-GA 属于体硅 CMOS 器件,空间应用时主要受到总剂量效 应和单粒子效应的影响。单粒子效应包括单粒子闩锁 (SEL, single event latch-up)、单粒子翻转 (SEU, single event upset)、单粒子功能中断 (SEFI, single event function interruption) 和单粒子功能失效 (SEF, single event failure)[10-12]。SEL 是指单个粒子入射产生的电荷触发了器 件内部的寄生 P-N-P 结构电流正反馈,最终导致器件烧毁。 SEU 是指单个粒子入射引起电荷沉积导致的存储单元状态 翻转。SEFI 是指器件中的特殊存储单元发生 SEU 后导致器 件功能丧失,如 SelectMAP SEFI、FAR SEFI及 POR SEFI 等。SEF 是指用户逻辑电路中的存储单元(主要指触发器 Flip-Flop 和 BRAM) 或配置存储器发生 SEU 造成用户功能 电路错误或者失效。SEFI 和 SEF 都是器件内部的存储单元 发生 SEU 对电路功能造成影响,区别在于存储单元的类型 和所属电路功能不同。

SRAM型 FPGA 空间应用时,用户主要关心器件所加载的用户功能电路在轨发生 SEF 的概率。导致用户电路失效的来源主要包括 CRAM、BRAM、用户 Flip-Flop 和特殊电路寄存器发生的单粒子翻转。CRAM 发生单粒子翻转可能导致查找表(LUT)、CLB、路由矩阵、布线开关等发生变化,造成电路逻辑错误或互联线桥接错误,引起工作电流增加,此外,SEU 在用户逻辑电路中通过故障耦合和

传递,最终导致用户电路输出错误、功能异常甚至功能中断。CRAM 的单粒子翻转在 FPGA 全部单粒子翻转事件中占 90%至 95%,是器件发生 SEF 的主要原因。BRAM 一般用于存储用户电路运算过程中产生的大量数据或参与计算的参数。根据数据更新频率的快慢,单粒子翻转导致电路运算结果错误的持续时间存在差异。用户 Flip-Flop 用于实现控制电路中的寄存器或少量数据寄存,发生单粒子翻转可能导致电路状态异常或者运算数据错误。NASA 给出了 SRAM 型 FPGA 单粒子功能失效率(SEF)的计算公式[5]:

$P(fs)_{\mathrm{error}} \propto P_{\mathrm{Configuration}} + P(fs)_{\mathrm{Functional Logic}} + P_{\mathrm{SEFI}}$  (1) 其中:  $P_{\mathrm{Configuration}}$  是配置存储器翻转导致的失效率; $P(fs)_{\mathrm{Functional Logic}}$ 是用户逻辑电路翻转导致的失效率,主要来源是用户 Flip-Flop 的单粒子翻转和组合逻辑的单粒子瞬态被后续寄存器捕获后产生的翻转; $P_{\mathrm{SEFI}}$ 是器件发生 SEFI 导致的失效率,概率极低。可以看出,CRAM、BRAM 和用户Flip-Flop 发生的单粒子翻转是导致器件功能失效的主要因

素,是单粒子翻转防护设计的重点对象。

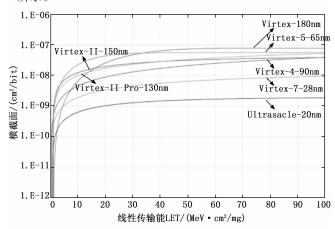

国内外学者开展了大量针对 Xilinx 公司的 SRAM 型 FPGA 器件单粒子效应的地面模拟辐照试验。在美国国家 航空航天局 NASA 针对商用现货(COTs,commercial off-the shelfs)器件编写的器件辐射环境选用指南[13]中,将 Xilinx 的 SRAM型 FPGA 器件的单粒子效应指标数据进行了整理归纳。如图 2 所示,该图为在重离子加速器试验中获取的 SEU 韦布尔曲线,主要覆盖了制造工艺特征尺寸在 180 nm~16 nm 范围的 SRAM型 FPGA 器件。从图中可以看出,工业级器件的单粒子翻转效应的线性传输能(LET, linear energy transfer)阈值均小于 3 MeV·cm²/mg,不能满足在轨单粒子翻转指标要求,需对该类器件进行加固设计[14-16],并对加固的有效性进行准确评估。上述器件 CRAM 在地球同步轨道(GEO)上的 SEU 概率如表 1 所示。

图 2 Xilinx 的主要 SRAM 型 FPGA 器件的配置存储器单粒子翻转试验数据<sup>[13]</sup>

| 类型            | 制造工艺         | 配置存储区容量       | 翻转率(/bit • day)        |

|---------------|--------------|---------------|------------------------|

| Virtex-II-pro | 130 nm bulk  | 34 292 768    | $3.56 \times 10^{-7}$  |

| Virtex-4      | 90 nm bulk   | 47 856 512    | $2.98 \times 10^{-7}$  |

| Virtex-5      | 65 nm bulk   | 82 696 192    | 5. $74 \times 10^{-7}$ |

| Virtex-7      | 28 nm bulk   | 447 337 216   | 1. $33 \times 10^{-7}$ |

| UltraScale    | 20nm bulk    | 1 031 731 104 | $2.77 \times 10^{-8}$  |

| UltraScale+   | 16 nm FinFET | 906 547 008   | $5.79 \times 10^{-9}$  |

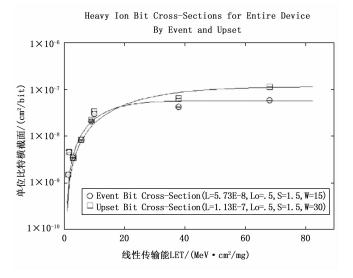

Virtex-5 系列包含字航级与工业级器件。字航级器件型 号为 XQR5VFX130T,采用三模冗余、单粒子瞬态滤波、 12 管 DICE 结构锁存单元等多种 SEU 加固技术,能够满足 空间应用高可靠要求。Xilinx公司联合美国喷气推进实验室 JPL、波音公司等机构联合开展了宇航级 Virtex-5 系列器件 的辐照试验。试验结果表明宇航级器件 CRAM 的单粒子 翻转率 (GEO 轨道) 小于 10<sup>-10</sup>次/比特·天, SEFI 概率 小于 2.76×10<sup>-7</sup>次/器件 • 天<sup>[17]</sup>。该系列器件已被应用于 美国 宇 航 局 开 发 的 高 性 能、可 重 构 数 据 处 理 系 统 SpaceCube2.0 中。国外 Heather Quinn 等[18] 开展了 Virtex-5 商业级器件的高能粒子辐照试验研究。试验对象为商业 级器件 XC5VLX50, 获得了重离子饱和翻转截面为 5.73×  $10^{-8}$  cm<sup>2</sup>/bit, 质子饱和翻转截面为 8.61× $10^{-14}$  cm<sup>2</sup>/bit, 利用韦布尔拟合方式获得曲线如图 3 所示。NASA 出具的 报告也给出了工业级器件的 CRAM 在 GEO 轨道的 SEU 概 率和 SEL 的大致数据范围,但未能提供具体的测试方法及 对 SEF 的评估结果。国内没有查到关于 Virtex-5 系列 FP-GA 的单粒子效应辐照试验数据。因此,为评估该器件空 间应用的可靠性,需要开展该器件的单粒子效应地面模拟 评估试验研究,特别是开展基于典型应用电路的 SEF 研 究, 指导航天器电子设备元器件选用和抗辐照加固设计。

图 3 XC5VLX50 重离子试验韦布尔曲线[18]

本文针对 Xilinx 公司工业级 Virtex-5 系列 SRAM 型

FPGA 开展了单粒子效应地面辐照试验方法研究,提出了CRAM 和 BRAM 的单粒子翻转测试方法,设计典型电路,开展了三模冗余设计前后 SEF 测试。通过设计单粒子效应测试系统,并参照 QJ 10005-2008《宇航用半导体器件重离子效应试验指南》的相关规定开展重离子辐照试验,获得了 Virtex-5 器件的 SEU、SEF 和 SEL 试验数据。最后利用空间环境模拟软件针对 GEO 轨道进行了在轨翻转率分析计算,可为该器件的空间应用提供基础数据。

# 1 试验方法

## 1.1 辐射源

国内可开展地面重离子辐照试验的试验装置主要有中国近代物理研究所的 HIRFL 回旋加速器和中国原子能科学院的 HI-13 串列静电加速器。根据被测器件硅衬底厚度和粒子射程,选择回旋加速器的 Ta 粒子开展 SEL 试验,选择串列加速器的 C、O和 F 粒子开展 SEU和 SEF 试验。试验所用粒子信息如表 2 所示。

表 2 Virtex-5 SRAM 型 FPGA 重离子辐照试验用粒子信息

| 离子种类 | 总能量<br>/MeV | Si 中射<br>程/μm | Si 中 LET/<br>(MeV・cm²<br>/mg) | 试验装置              | 试验<br>类型    |

|------|-------------|---------------|-------------------------------|-------------------|-------------|

| Ta   | 2262.5      | 83.3          | 81.35                         | HIRFL 回旋加速器       | SEL         |

| С    | 80          | 127           | 1.73                          | HI-13 串列<br>静电加速器 | SEU、<br>SEF |

| О    | 103         | 99. 4         | 3. 1                          | HI-13 串列<br>静电加速器 | SEU,<br>SEF |

| F    | 115         | 87. 9         | 4. 427                        | HI-13 串列<br>静电加速器 | SEU,<br>SEF |

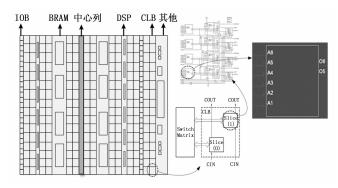

图 4 Virtex5 系列 FPGA 整体结构及内部 CLB 结构简图 [19]

### 1.2 试验对象

Virtex-5 器件采用 65 nm 铜 CMOS 工艺,内核电压为 1.0 V。Virtex-5 系列 SRAM 型 FPGA 器件架构示意图如图 4 所示。本文试验对象为 XC5VFX130T-1FFG1738I,该器件内部集成了 20 480 个 CLB Slice (可提供 81 920 个用户 Flip-flop 或最大 1 580 Kb 分布式 RAM)、320 个 25×18位的 DSP48E、228 个 36 Kb 的 Block RAM 和其他一些硬核资源[20]。XC5VFX130 器件的各类资源组成如表 3 所示。

|    |          |      |            | _             |

|----|----------|------|------------|---------------|

| 主っ | Virtor-5 | 交 石山 | XC5VFX130T | 界 / 井 / 井 / 上 |

|    |          |      |            |               |

| CLB Flip-Flops         | 81 920 |

|------------------------|--------|

| CLB LUT                | 81 920 |

| 分布式 RAM 最大容量(Kb)       | 1 580  |

| Block RAM(36 Kb/个)     | 298    |

| Block RAM 总容量(Kb)      | 10 728 |

| CMTs                   | 6      |

| Ethernet MACs          | 6      |

| 用户 I/Os 最大数量(最大 1.8 V) | 840    |

| DSP slices             | 320    |

| PowerPC 处理器核           | 2      |

| PCIe                   | 3      |

| GTX 6.5 Gb/s 收发器       | 20     |

|                        |        |

被测器件为倒装器件,重离子人射时会穿过衬底区域,导致无法到达芯片敏感区或由于能量损耗影响有效 LET 值的准确性。试验前需要对待测器件进行开帽及衬底减薄处理,如图 5 所示。开帽处理的目的是将芯片或器件的封装罩(通常是塑料封装或金属封装)去除,减薄的目的是使得重离子更容易进入并与器件内部相互作用。要保证开帽减薄后的器件外部引出端和内部引线未受到损伤,电性能测试功能及电流正常。在本次试验中,减薄后芯片衬底到敏感区距离约为  $70~\mu m$ 。

图 5 DUT 减薄前后照片

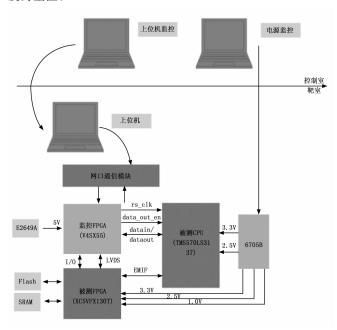

# 1.3 单粒子效应检测装置组成

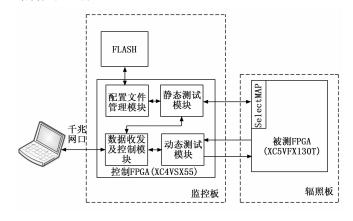

单粒子效应检测系统由上位机软件、监控芯片载板和DUT 载板组成。上位机软件作为测试系统控制中心与数据存储分析平台,完成测试项目、测试模式、测试数据、参数设置和人机交互。远程控制监控芯片完成对自身功能参数的设置及对被测芯片的配置、测试和数据上传,并对上传数据进行分析和显示。监控芯片载板与上位机之间基于UDP协议的高速网络连接,以达到高速可靠的数据交互和板间连线最少化的双重目的。监控器件型号为 XC4VSX55,作为主控器件通过 SelectMAP 端口对 DUT 进行器件配置、刷新和回读,同时使用 LVDS 接口作为与 DUT 动态测试电路之间的接口,控制 DUT 的测试模式、产生测试用输入数据并接收 其测试结果数据。DUT 载 板 的 核 心器 件为XC5VFX130T,电压域包括 3.3 V、2.5 V 和 1.0 V,由桌面电源进行单独供电。单粒子效应检测系统整体设计方案

结构如图 6 所示。

图 6 SRAM型 FPGA 单粒子效应测试系统结构示意框图

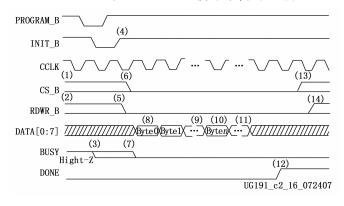

监控芯片载板上的核心器件为 XC4VSX55,主要功能模块包括配置文件管理模块、静态测试模块、动态测试模块和数据收发控制模块。配置文件管理模块负责从 FLASH读取位流文件。静态测试模块实现对被测 FPGA 进行加载和回读的功能。动态测试模块实现向被测 FPGA 发送输入数据和接收输出数据的功能。数据收发控制模块实现静态数据与动态数据的分析和与上位机之间的数据交互功能。其中静态测试模块通过 SelectMAP 口实现 CRAM 与BRAM 静态 SEU 数据回读,因此 SelectMAP 读写访问接口属于核心电路。按照器件手册要求,Virtex-5 系列SRAM型 FPGA的 SelectMAP口读写时序如图 7 所示[21]。

图 7 Virtex-5 系列 SRAM型 FPGA SelectMAP 口读写时序图 (8 比特模式)<sup>[21]</sup>

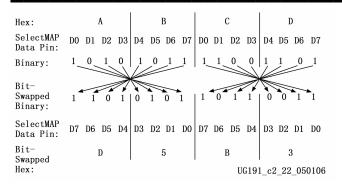

需要注意的是,从 FLASH 中读取的位流文件再写给 SelectMAP 口时,应该先进行高低位交换,如图 8 所示。即以 8 比特为单位,将 D0 位赋给 D7 位,D1 位赋给 D6 位,以此类推,D7 位赋给 D0 位。

#### 1.4 单粒子效应检测装置搭建

辐照试验时,单粒子效应测试系统搭建于设有高能重 离子辐照终端的靶室内,试验人员通过位于控制室的两台 笔记本对靶室内的上位机与桌面电源进行远程控制。试验

图 8 SelectMAP 口配置数据高低位交换说明<sup>[21]</sup>

装置连接关系如图 9 所示。试验系统搭建好后,束流终端 利用红外线进行定位,将束流对准 DUT 且完全覆盖芯片。 位于中国原子能科学院真空罐内的 DUT 如图 10 所示。整 个试验中, 粒子入射方向均采用垂直于样品方向, 试验温 度为室温。

图 9 试验系统连接关系示意图

图 10 真空罐中的被测 FPGA 芯片

#### 1.5 单粒子效应测试方法

#### 1.5.1 SEU测试方法

SEU测试的目标是检查被测器件中 CRAM 和 BRAM 的 SEU 响应,采用静态测试方法,即先对 DUT 加载配置 文件,然后开始辐照。在辐照过程中,会关闭用户逻辑电 路的工作时钟,并且复位信号一直有效,使用户逻辑电路 处于静止状态,这样可以避免单粒子瞬态效应被电路捕获 引入不真实的 SEU。在辐照前,对被测器件进行回读并保 存数据作为参考。当 DUT 结束辐照后, 其状态会与初始状 态进行比较,以获取静态翻转计数。

在 FPGA 配置完成后,将工作时钟暂停,然后对器件 进行辐照,辐照量可以事先指定,或者直到出现需要停止 辐照的条件。按照业界标准,本次试验结束的条件是总注 量达到 1×10<sup>7</sup> 个/cm<sup>2</sup> 或者 SEU 次数达到 1 000 次。通常需 要通过累积多次较短的辐照注量来达到试验结束条件,以 避免导致停止辐照的条件提前出现。此外,当 SEU 数量达 到一定程度导致芯片温度超过安全阈值或工作电流超过安 全范围时,辐照过程就会被停止。

一旦束流关闭,就会向 FPGA 发送一个"捕获"命令, 该命令将 CRAM 和 BRAM 的数据通过 Select MAP 口读出 并发送至监控芯片。然后,监控芯片通过对比回读数据与 初始数据来统计翻转数量。

### 1.5.2 SEF 测试方法

在 SEF 测试中,采用动态测试来评估单粒子轰击对用 户电路的实时影响。静态测试中被测器件处于静止状态并 施加辐射,而动态测试则是在被测器件所加载的功能电路 在正常工作过程中暴露于辐射之下。即在动态测试过程中, FPGA 会以预定的工作时钟和输入数据进行操作。当重离 子与 FPGA 相互作用时,可能引起功能电路发生 SEF。动 态测试以真实工况为条件,可以更真实地评估 FPGA 功能 电路对 SEF 的敏感性,达到识别潜在的单粒子翻转敏感电 路和设计更健壮的错误检测和纠正机制的目的。

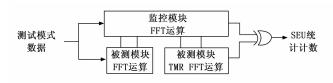

本次试验所采用的 SEF 的动态测试方法,具体是向 DUT 加载用户电路,并使用户电路处于工作状态,然后开 始辐照,监测用户电路的输出数据,与预期结果进行对比 和进行 SEU 次数统计。连续 10 秒输出数据持续错误时停止 辐照,统计记录一次 SEF。用户电路为输入数据宽度为 32 位,数据深度为32位的16384点FFT浮点运算模块。为同 时对三模冗余加固效果进行评估,在 DUT 中还新增一组采 用相同数据源和相同配置的三模冗余 FFT 运算模块。监控 FPGA 中实现相同配置的 FFT 浮点运算模块,与 DUT 中 的运算结果进行对比。FFT 测试电路结构如图 11 所示。

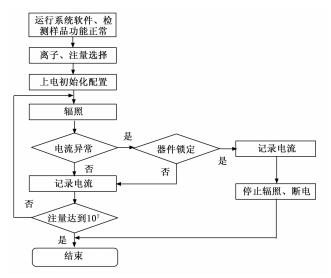

#### 1.5.3 SEL 测试方法

SEL 的试验主要目的是为获取单粒子闩锁阈值,因此 采用较大 LET 能量的 Ta 粒子作为辐射源。在测试中,向 DUT 加载典型配置程序使其处于正常的工作状态,其余设 置参照 SEF 测试,需要额外增加程控电源对电流进行实时

图 11 FFT 测试基本通道结构示意图

监控。为确保电流的增加是由 SEL 导致而不是由于 SEU 累 计造成的电流功能异常,在观测到大电流后,先关闭辐射 束流,然后进行重加载。

在本次试验中,发生 SEL 的判据为 DUT 的工作电流 增大至正常工作电流的 2 倍,同时用户电路功能中断,且 无法通过重加载恢复电路功能和正常电流,必须通过加断 电来消除大电流。试验结束条件为总注量达到 1×10<sup>7</sup> 个/cm²或者发生一次 SEL。发生 SEL 后,需立即切断供电以保护器件不受大电流影响造成硬损伤。

SEL 测试流程如图 12 所示,具体流程如下:

- 1) 选择粒子种类和注量率,对系统进行上电初始化配置:

- 2) 运行典型功能程序;

- 3) 开始辐照;

- 4) 检测电流异常,判断器件是否闩锁(数值为正常电流的2倍值):如果否,跳转5);如果是,跳转6);

- 5) 记录电流数值,并继续辐照至离子注量达到结束值,跳转7);

- 6) 通过复位或重加载操作电流若可以恢复,则跳转至5),若无法恢复,则认为器件锁定,此时记录电流,停止辐照,并切断器件电源;

- 7) 试验结束。

图 12 SEL 测试流程图

### 2 试验结果及分析

采用 LET 值为  $1.73\sim4.43~\text{MeV} \cdot \text{cm}^2/\text{mg}$  的 C、O 和 F 离子对器件进行 SEU 测试辐照。每个粒子辐照完成后,

会利用 SelectMap 总线回读出当前待测 FPGA 的 CRAM 数据,并与原始配置比特文件进行对比,统计出有差异的数据个数,即为发生翻转的总次数。试验得到的 CRAM 及BRAM 的 SEU 测试数据分别如表 4 和表 5 所示。

表 4 XC5VFX130T 配置存储器的 SEU 测试数据

| 离子种类 | LET 值<br>(MeV·cm²/mg) | 注量率<br>(个/cm² • s) | 总注量 N<br>(个/cm²)  | SEU 次数<br>N <sub>upsets</sub> |

|------|-----------------------|--------------------|-------------------|-------------------------------|

| F    | 4.427                 | 520                | $3 \times 10^{4}$ | 2 587                         |

| F    | 4.427                 | 520                | $3 \times 10^{4}$ | 2 558                         |

| F    | 4.427                 | 520                | $3 \times 10^{4}$ | 2 952                         |

| F    | 4.427                 | 520                | $3 \times 10^{4}$ | 2 759                         |

| О    | 3. 1                  | 970                | $3 \times 10^{4}$ | 2 438                         |

| С    | 1.73                  | 470                | $3 \times 10^{4}$ | 1 027                         |

| С    | 1.73                  | 470                | $3 \times 10^{4}$ | 881                           |

表 5 XC5VFX130T BRAM 的 SEU 测试数据

| 离子 种类 | LET 值<br>(MeV•cm²/mg) | 注量率<br>(个/cm² • s) | 总注量 N<br>(个/cm²)  | SEU 次数<br>N <sub>upsets</sub> |

|-------|-----------------------|--------------------|-------------------|-------------------------------|

| F     | 4.427                 | 520                | $3 \times 10^{4}$ | 2 532                         |

| F     | 4.427                 | 520                | $3 \times 10^{4}$ | 2 418                         |

| F     | 4.427                 | 520                | $3 \times 10^{4}$ | 3 532                         |

| F     | 4.427                 | 520                | $3 \times 10^{4}$ | 2 600                         |

| О     | 3. 1                  | 970                | $3 \times 10^{4}$ | 2 170                         |

| С     | 1.73                  | 470                | $3 \times 10^{4}$ | 1 043                         |

| С     | 1.73                  | 470                | $3 \times 10^{4}$ | 1 165                         |

为获取器件存储区在轨评估数据,需计算出重离子辐照下各类存储资源的单粒子翻转截面。CRAM与 BRAM 的每比特静态翻转截面  $\sigma_{see}$ 的计算公式如下:

$$\sigma_{\text{seu}} = N_{\text{upsets}} / (F \cdot N \cdot \sin \theta) \tag{2}$$

式中, $N_{\text{upset}}$ 为 SEU 次数,即为试验中统计的各类存储资源的翻转数据结果;F 为器件存储单元数量,该器件的 CRAM 数量为 49 234 944 个,BRAM 单元数量为 15 140 480 个[20]; $N \cdot \sin\theta$  为离子入射的有效总注量,其中,N 为试验设定的辐射粒子源的总注量,倾角  $\theta$  为入射离子束与器件平面的夹角,本试验为垂直入射,因此  $\theta$  为 90°。

按照公式 (2) 对 CRAM 与 BRAM 的 SEU 测试数据进行处理,可得到静态翻转截面数据如表 6 所示。

表 6 CRAM 与 BRAM 的静态翻转截面

| 离子 | LET 值/(MeV·          | CRAM 翻转                                     | BRAM 翻转截面                                 |

|----|----------------------|---------------------------------------------|-------------------------------------------|

| 种类 | cm <sup>2</sup> /mg) | 截面 σ <sub>seu</sub> /(cm <sup>2</sup> /bit) | $\sigma_{\rm seu}/({\rm cm}^2/{\rm bit})$ |

| F  | 4. 427               | $2.35 \times 10^{-9}$                       | 8. $61 \times 10^{-9}$                    |

| О  | 3. 1                 | 2. $11 \times 10^{-9}$                      | 6.74 $\times$ 10 <sup>-9</sup>            |

| С  | 1.73                 | $8.26 \times 10^{-10}$                      | $3.43 \times 10^{-9}$                     |

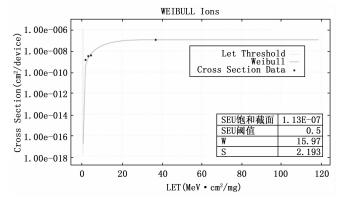

利用本试验获得的 CRAM 的 SEU 截面,结合文献 [9] 给出的饱和截面,进行韦布尔拟合,得到 CRAM 翻转截面与 LET 值的拟合曲线如图 12 所示。其中,韦布尔

曲线的关键表征参数为:饱和截面为  $1.13\times10^{-7}$  cm²/bit,翻转 LET 阈值为 0.5 MeV·cm²/mg,形状参数 W 为 15.97 MeV·cm²/mg,指数参数 S (无量纲)为 2.193。以上数值与文献 [18] 所得数据量级一致,进一步验证了本次试验所采用的方法有效且准确。

利用所得的韦布尔拟合参数和 CREME96 模型,使用空间环境模拟软件 Omere 对在轨翻转概率进行计算。结果如表 7 所示。轨道环境选择 GEO 轨道,太阳状态处于平静期(Solar min),屏蔽层为厚度 100 mils 的铝材料,计算结果为 CRAM 的 SEU 概率为 6.41×10<sup>-7</sup>次/比特·天。该结果显示工业级器件的 CRAM 翻转概率比宇航级器件低 3 个数量级,这进一步说明,COTs 器件在空间应用时,必须重视单粒子翻转敏感性并对其采取多种类、有针对性的加固措施。

图 13 XC5VFX130T 配置存储区威布尔拟合曲线及参数

表 7 XC5VFX130T 配置存储器在轨翻转率 (GEO,太阳平静期,100 mils 铝屏蔽,CREME96)

| 单位    | CRAM 的 SEU 概率/次       |

|-------|-----------------------|

| 每器件每天 | 31.6                  |

| 每比特每天 | $6.41 \times 10^{-7}$ |

SEF 试验中被测器件加载的典型应用电路为 FFT 浮点运算。采用 O 粒子进行辐照,监测功能中断次数,并根据公式(2)计算得到典型应用电路的 SEF 截面。再利用公式(3)计算得到加固倍数。

$$\mu = \frac{\sigma_{\text{sefl}}}{2} \tag{3}$$

式中, $\mu$ 表示加固倍数,加固倍数越大,反映加固措施效果越好。 $\sigma_{\text{sefl}}$ 表示加固前的典型电路 SEF 截面, $\sigma_{\text{sefl}}$ 表示加固后的典型电路 SEF 截面。

FFT 浮点运算模块的 SEF 试验数据如表 8 所示。

表 8 FFT 浮点运算模块试验结果

|    |                      |                                     | 三模后 SEF 截面                               |      |

|----|----------------------|-------------------------------------|------------------------------------------|------|

| 种类 | cm <sup>2</sup> /mg) | $\sigma_{\rm sefl}/({\rm cm}^2/器件)$ | σ <sub>sef2</sub> /(cm <sup>2</sup> /器件) | 数 μ  |

| О  | 3. 1                 | 9.37 $\times$ 10 <sup>-6</sup>      | $1.97 \times 10^{-6}$                    | 4.76 |

FFT 浮点运算模块的 SEF 截面为 10<sup>-6</sup>量级,三模后 SEF 截面相对于三模前下降了 22%,即仅采用三模措施时的加固效果为 4.8 倍。由于三模冗余是一种容错措施,可以屏蔽三模电路其中一模电路的单粒子翻转错误,但是随着单粒子翻转累积导致另外一模电路也发生错误,三模冗余电路将无法产生正确的判决结果,导致三模冗余措施失效。因此,三模冗余措施必须结合刷新措施一起使用。利用刷新措施及时纠正 CRAM 的 SEU,避免 SEU 累积导致两模电路同时错误的情况发生。

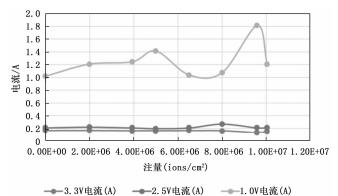

SEL 试验采用 LET 值为 81. 35 MeV·cm²/mg 的 Ta 离子对被测器件进行辐照,直到离子总注量达到 1×10<sup>7</sup> 个/cm²。辐照过程中监测 3.3 V、1.2 V 和 1.0 V 电压域的电流变化情况,如图 14 所示。1.0 V 为器件核压,其工作电流有异常增大现象,但电流没有达到正常工作电流的两倍,且电流到达 1.8 A 后迅速降至 1.0 A。经分析该电流异常现象可能是由于单粒子翻转导致。试验数据表明该器件单粒子闩锁阈值大于 81. 35 MeV·cm²/mg。

图 14 FPGA SEL 试验过程电流变化图

### 3 结束语

Virtex-5 系列 FPGA 采用 65 nm 工艺, 经重粒子辐照试验验证,该系列器件的单粒子闩锁阈值大于 81.35 MeV·cm²/mg, CRAM 的 SEU 阈值小于 1.73 MeV·cm²/mg, 采用 CREME96 模型,考虑太阳平静期,100 mils铝屏蔽时,GEO 轨道 CRAM 每比特翻转概率为 6.41×10<sup>-7</sup>次/天,每器件翻转率为 31.6 次/天。试验结果表明该器件属于单粒子翻转敏感器件。本文对三模冗余措施的加固效果进行了评估,结果说明仅采用三模措施加固效果不明显,建议与刷新措施结合使用。

#### 参考文献:

- [1] 范占春,董世林,鲁 帆,等. 一种星载多功能可重构终端设计[J]. 计算机测量与控制,2022,30(4):149-154.

- [2] ZHEN G, JINHUA Z, TONG Y, et al. Fault tolerant design of large-scale digital beam forming in SRAM-FPGAs for software defined satellite platforms [J]. China Communications, 2020,

- 7:67-79.

- [3] 王伟伟, 闫新峰, 修 展, 等. 基于 FPGA 的在线重构设计方法 [J]. 计算机测量与控制, 2020, 28 (12): 213-216.

- [4] 何怡刚, 赵 明, 周健波, 等. 一种模拟单粒子瞬态产生和测量方法 [J]. 计算机测量与控制, 2020, 28 (10): 51-54.

- [5] SHUAI G, XIN-YU L, SHI-WEI Z, et al. Heavy ion-induced MCUs in 28nm SRAM-based FPGAs: upset proportions, classifications and pattern shapes [J]. Nuclear Science and Techniques, 2022, 33 (161): 1-10.

- [6] 李 鑫, 闫雪梅, 高媛媛, 等. FPGA 发展现状和行业应用分析 [J]. 产业与政策, 2022 (7): 65-72.

- [7] 邢克飞,杨 俊,王跃科,等. Xilinx SRAM型 FPGA 抗辐射设计技术研究[J]. 宇航学报,2007(1): 123-129.

- [8] KOGA R, GEORGE J, SWIFT G, et al. Comparison of Xilinx Virtex-II FPGA SEE sensitivities to protons and heavy ions [J]. IEEE Transactions on Nuclear Science, 51 (5): 2825 -2833.

- [9] LILI D, ZHONGMING W, WEI C, et al. Bitstream-based simulation for configuration SEUs in Xilinx Virtex-4 FPGAs [C] // 2016 16th European Conference on Radiation and Its Effects on Components and Systems (RADECS), IEEE, 2016.

- [10] DAVID S L, GREGORY R A, GARY S, et al. Single-Event Characterization of the 20 nm Xilinx Kintex UltraScale Field-Programmable Gate Array under Heavy Ion Irradiation [C] // 2015 IEEE Radiation Effects Data Workshop (REDW), IEEE, 2015.

- [11] VLAGKOULIS V, SARIA, VRACHNIS J, et al. Single event effects characterization of the programmable logic of Xilinx ZYNQ-7000 FPGA using very/ultra high-energy heavy ions [J]. IEEE Transactions on Nuclear Science, 2021, 68 (1); 36 - 45.

- [12] MELANIE B, HAK K, ANTHONY P, et al. Xilinx Kintex-Ultrascale Field Programmable Gate Array Single Event

- Effects (SEE) Heavy-ion Test Report [R/OL]. [2023-06-07]. https://ntrs. nasa. gov/api/citations/20205007765/downloads/20205007765.pdf.

- [13] ADELL P, ALLEN G, ASBURY C, et al. Guideline for the selection of COTS electronic parts in radiation environments [Z]. JPL Publication, 2019, 19-9.

- [14] 杨 亮,李 祁. 基于三模冗余架构的航天器 FPGA 可靠性设计 [J], 计算机测量与控制, 2019, 27 (12): 244-248;

- [15] VASILEIOS V, AITZAN S, GEORGIOS A, et al. Configuration Memory Scrubbing of SRAM-Based FPGAs Using a Mixed 2-D Coding Technique [J]. IEEE Transactions on Nuclear Science, 2022, 69 (4): 871 - 882.

- [16] PIERRE M, YANRAN P C, JASON V, et al. Radiation-Tolerant Deep Learning Processor Unit (DPU) -Based Platform Using Xilinx 20-nm Kintex UltraScale FPGA [J]. IEEE Transactions on Nuclear Science, 2023, 70 (4): 714-721.

- [17] SWIFT G, CARMICHAEL C, ALLEN G, et al. Compendium of XRTC radiation results on all single-event effects observed in the Virtex-5QV [Z/OL]. [2023-06-07]. https://nepp.nasa.gov/respace\_mapld11/talks/tue/MAPLD/1420% 20-% 20Swift.pdf.

- [18] HEATHER Q, HEITH M, PAUL G, et al. Static proton and heavy ion testing of the Xilinx Virtex-5 device [C] // 2007 IEEE Radiation Effects Data Workshop, IEEE, 2007.

- [19] 赖晓玲, 贾 亮, 朱 启. 面向航天应用的 Virtex5 系列 FP-GA 单粒子翻转防护技术 [J]. 空间电子技术, 2017 (3): 85 -91.

- [20] Xilinx. Virtex-5 FPGA Family Overview [DB/OL]. [2016-4-12]. http://www.xilinx.com/support/documentation/datasheets/ds174.pdf.

- [21] Virtex-5 FPGA Configuration User Guide [Z/OL]. [2023-06-07]. https://docs.xilinx.com/v/u/en-US/ug191.

- [12] 黄亭飞,程光权,黄魁华,等. 基于 DQN 的多类型拦截装备 复合式反无人机任务分配方法 [J]. 控制与决策,2022,37 (1):142-150.

- [13] 邓恒玮. 基于强化学习的无人机网络的资源分配和路径规划 [D]. 成都: 电子科技大学, 2022.

- [14] 周翔龙. 基于强化学习的无人机飞行编队频谱分配技术研究 [D]. 哈尔滨:哈尔滨工程大学,2020.

- [15] 朱星宇. 基于任务的无线网络资源分配技术 [D]. 成都: 电子科技大学,2020.

- [16] 李冬雪. 基于深度强化学习的资源分配问题研究 [D]. 北京: 北京交通大学, 2021.

- [17] SCHULMAN J, LEVINE S, ABBEEL P, et al. Trust region policy optimization [C] //International conference on machine learning, PMLR, 2015: 1889 1897.

- [18] SCHULMAN J, WOLSKI F, DHARIWAL P, et al. Proximal policy optimization algorithms [J]. arXiv preprint arXiv: 1707.06347, 2017.

- [19] RUDER S. An overview of gradient descent optimization algorithms [J]. arXiv preprint arXiv: 1609.04747, 2016.

- [20] 李兴怡,岳 洋. 梯度下降算法研究综述 [J]. 软件工程, 2020, 23 (2): 4.

- [21] 赵佳楠, 胡晓辉, 杜欣欣. 基于近端策略优化算法的车载边缘计算网络频谱资源分配 [J]. 数据与计算发展前沿, 2022, 4 (4): 142-155.

- [22] ARIVUDAINAMBI D, REKHA D. Broadcast scheduling problem in TDMA ad hoc networks using immune genetic algorithm [J]. International Journal of Computers Communications & Control, 2013, 8 (1): 18-29.