文章编号:1671-4598(2021)05-0179-05

DOI:10.16526/j. cnki.11-4762/tp.2021.05.036

中图分类号:TP274

文献标识码:A

# 基于石英挠性加速度计 A/D 与 I/F 数据采集系统的对比研究

### 祛志豪,李锦明

(中北大学 仪器与电子学院,太原 030051)

摘要:为满足对寻北仪导航系统中加速度计采集数据的高精度要求,提出了基于石英挠性加速度计的 A/D 采集系统与 I/F 数据采集系统的对比研究;系统采用了高精度 A/D 转换芯片 AD7693 和 V/F 高精度转换芯片 LM331 分别对石英挠性加速度计采集的数据进行处理转换,以 FPGA 芯片 XC7Z020 为逻辑控制核心对转换的数据进行编帧处理,通过 RS232 总线将处理的数据发送到上位机;测试结果表明,在相同条件下,I/F 采集系统转换的精度 99.99%优于 A/D 采集系统转换的精度 98.7%;短时间内,I/F 采集系统采集的数据变化不大,A/D 采集系统采集的数据变化大,所以 I/F 采集系统稳定性更好。

关键词:石英挠性加速度计;A/D采集;I/F采集;上位机

## Comparative Study of A/D and I/F Data Acquisition System Based on Quartz Flexible Accelerometer

Zhang Zhihao, Li Jinming

(School of Instrument and Electronics, North University of China, Taiyuan 030051, China)

Abstract: In order to meet the high—precision requirements of accelerometer data acquisition in the navigation system of north finder, a comparative study of A/D acquisition system based on quartz flexible accelerometer and I/F data acquisition system is proposed. The system uses the high—precision A/D conversion chip AD7693 and the V/F high—precision conversion chip LM331 to process and convert the data collected by the quartz flexible accelerometer, and use the FPGA chip XC7Z020 as the logic control core to frame the converted data. Send the processed data to the host computer through the RS232 bus. The test results show that under the same conditions, the conversion accuracy of the I/F acquisition system is 99.99% better than that of the A/D acquisition system conversion accuracy of 98.7%; in a short time, the data collected by the I/F acquisition system does not change much. The data collected by the D acquisition system varies greatly, so the I/F acquisition system has better stability.

Keywords: quartz flexible accelerometer; A/D acquisition; I/F acquisition; host compute

#### 0 引言

随着惯性导航系统技术的飞速发展,人们对导航系统高精度精准定位提出了越来越高的要求 高传统加速度计 受温度影响大,抗干扰能力差,精度低;为了提高定位的精确度,系统采用石英挠性加速度计,该加速度计具有高精度,抗干扰能力强的特点,是惯性导航系统和指导系统中不可缺少的关键器件之一。在寻北仪导航系统中,为了提高对加速度计采集数据的转换精度,系统采用 A/D 转换与 I/F 转换两种电路分别对加速度计采集的数据进行转换。 I/F 转换技术是将电流信号转换成电压信号,然后将电压信号转换成频率信号,该技术的特点是:转换范围大,转换精度高,受温度影响小,适用于中、高精度惯导系统; A/D 采集系统与 I/F 采集系统相比,它的功耗低,电路结构简单。两种系统将各自采集的加速度数据送至 FPGA 进行数

据处理、编帧,最后通过串口发送到上位机进行显示比较 两种系统的转换精度、稳定性。

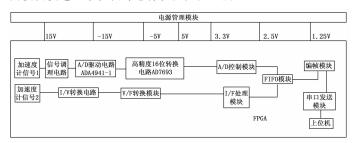

#### 1 系统硬件设计

系统硬件部分主要由 FPGA 芯片 XC7Z020 主控、2 路石英挠性加速度计信号、A/D 信号调理电路、A/D 驱动模块、A/D 转换模块、I/F 转换电路、V/F 转换模块等模块组成。软件部分主要由 A/D 控制模块、I/F 处理模块、FIFO 模块、编帧模块、串口发送模块组成。石英挠性加速度计通过信号调理电路以及 I/V 转换电路,将电流信号转换成电压信号,用于 A/D 模数转换以及 V/F 转换所需的电压信号;系统采用外部电源机给石英挠性加速度计提供+15 V,一15 V 以及一5 V 电源,采用电脑给系统板提供 5 V电源,通过稳压芯片 AMS1117—3.3、REF5025、REF3012将 5 V 转换成 3.3 V、2.5 V、1.25 V 直流电源,负责给所

收稿日期:2020-09-27; 修回日期:2020-10-29。

作者简介:张志豪(1996-),男,山西运城人,硕士,主要从事数据采编、存储方向的研究。

李锦明(1971-),男,重庆人,副教授,硕士生导师,主要从事动态测试、数据采编方向的研究。

引用格式:张志豪,李锦明. 基于石英挠性加速度计 A/D 与 I/F 数据采集系统的对比研究[J]. 计算机测量与控制,2021,29(5):179-183.

需模块供电。系统设计总体框图如图 1 所示。

图 1 系统总体框图

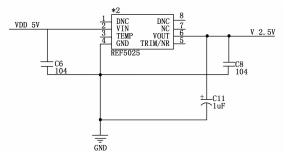

#### 1.1 A/D 参考电压源

系统采用石英挠性加速度计采集的数据,需要高精度的 A/D 转换器进行采集处理,而高精度 A/D 转换器完成数据转换需要稳定的参考电压源<sup>[2]</sup>。设计采用高精度稳压源REF3012 来生成 A/D 参考电压源,REF5025 的电压精度达到 0.05%,温度漂移最低达到 3 ppm/ °C; REF5025 的电压精度达到 0.05%,温度漂移最低达到 3 ppm/ °C。系统通过REF5025 将外部电源 5 V 转换成 2.5 V,作为 AD7693 最理想的参考电压基准源。A/D 参考电压源如图 2 所示。

图 2 A/D 参考电压源

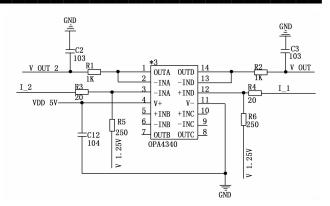

#### 1.2 信号调理电路

石英挠性加速度计输出的信号是电流信号,为了满足 A/D 转换要求,需要将电流信号转换成电压信号。由于加速度计输出的电流信号在-5 mA~+5 mA 之间进行变化,而 AD7693 的参考电压为 2.5 V,为了满足 A/D 采集的信号在 0~5 V 之间变化,系统采用 OPA4340 运算放大器进行调理,将加速度计的电流信号转换成电压信号,并将转换后的电压进行 1.25 V 的零位偏置,从而得到输入的电压范围为 0~2.5 V。OPA4340 主要完成电压跟随器的功能,该功能具有输入阻抗高、输出阻抗低的特点,在 OPA4340的输出端设置一个低通滤波器,该截止频率为 15 KHz,为了滤除高频信号对加速度计信号的干扰。信号调理电路如图 3 所示。

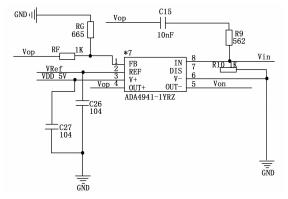

#### 1.3 A/D 驱动电路

为了提高 AD7693 的转换精度,系统采用 ADA4941-1 完成输入电压的驱动功能 海。将该驱动电路的额差分输出电压输出到 AD7693 的差分输入端。加速度计通过信号调理电路输出的电压范围为  $0\sim2.5~\mathrm{V}$ ,经过 ADA4941-1 的第

图 3 信号调理电路

8 引脚将加速度计信号输入到 A/D 驱动电路中,由图得, ADA4941-1 的第 4 引脚 OUT+为  $V_{op}$ ,第 5 引脚 OUT-为  $V_{om}$ 。施加到 REF 引脚不影响 OUT+引脚上的电压。因此,输出之间可能存在所需的输出共模电压。当计算输出电压时,必须同时考虑差分和共模输出电压来避免不可预想的差分偏移<sup>[4]</sup>。

$$V_{OP} = V_{IN}(1 + \frac{R_F}{R_G}) - V_G(\frac{R_F}{R_G}) \tag{1}$$

$$V_{ON} = -V_{IN}(1 + \frac{R_F}{R_G}) + V_G(\frac{R_F}{R_G}) + 2V_{REF}$$

(2)

则 ADA4941-1 的差分输出电压为:

$$V_{OP} - V_{ON} = 2V_{IN}(1 + \frac{R_F}{R_C}) - 2V_G(\frac{R_F}{R_C}) - 2V_{REF}$$

(3)

由此可见 A/D 驱动电路的差分输出电压与加速度计输出信号之间的关系。A/D 驱动电路如图 4 所示。

图 4 A/D 驱动电路

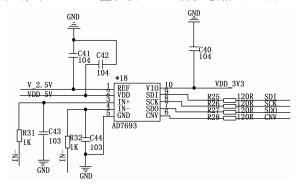

#### 1.4 A/D 转换电路

系统采用 AD7693 作为 A/D 数据采集系统的核心控制器件,该器件是 16 位、电荷再分配、差分输入、逐次逼近型的 A/D 模数转换器件 [5] ,该器件是与 ADA4941-1 驱动芯片配合使用,该系统的 A/D 采样频率为 300 kHz。设计中,AD7693 的 VDD 端接 5 V 电源,VIO 端接 3.3 V,REF 端接 2.5 V,IN+和 IN—两端分别接 ADA4941-1 的OUT+和 OUT—端,从而实现信号差分输入,SDI、SCK、SDO、CNV 分别与 FPGA 的引脚相连,在整个采样转换期

间,SDI 端一直处于高电平,SCK 端由 FPGA 提供 10 MHz 的时钟信号,AD7693 采样与否取决于 CNV 端,当 CNV 端处于高电平时,该器件对 IN+和 IN-端引脚之间的电压差进行采样,两引脚之间的电压差在 0 到  $V_{REF}$ 之间变化  $\mathbb{C}^{[6]}$ 。采样的值在  $0\sim2*V_{RFF}$ 变换,A/D 转换电路如图 5 所示。

图 5 A/D 转换电路

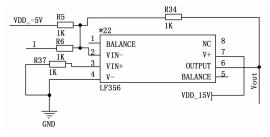

#### 1.5 I/V 转换电路

由于加速度计输出的是电流信号,为了得到所需的频率信号,需要将电流信号转换成电压信号<sup>[7]</sup>。系统采用LF356运算放大器,在LF356的VIN一端接加速度计电流信号以及-5V电源,然后将VIN一端和OUTPUT端连接,VIN+端接地。

$$V_{\text{OUT}} = 5 \times \frac{R_F}{R_E} - I \times R_F \tag{4}$$

由此设计出反向加法电路,当  $R_F$  和  $R_E$  都为 1 K 时,  $V_{\rm OUT}=5-I\times 1~000$ ,由于加速度计输出的电流信号为-5~5 mA,所以  $V_{\rm OUT}$ 的变化范围为  $0\sim 10~{\rm V}$ 。 $I/{\rm V}$  转换电路如图 6 所示。

图 6 I/V 转换电路

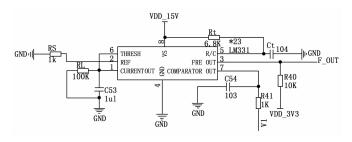

#### 1.6 V/F 转换电路

系统采用 LM331 将 LF356 输出的电压信号转换成 FP-GA 能够监测的周期脉冲信号,VS 电源端接 15 V,参考电压源接 0 V,THRESH 和 IOUT 端接下拉电阻,FOUT 端接 3.3 V 的上拉电阻,该器件温度漂移最大达到 50 ppm/ $^{\circ}$ C,输出频率最大范围为 1 Hz $^{\circ}$ 100 KHz $^{\circ}$ 8 。 V/F 转换电路如图 7 所示。

由图可得,

$$F_{\text{OUUT}} = \frac{V_{IN}}{2.09V} \cdot \frac{R_S}{R_L} \cdot \frac{1}{R_t C_t}$$

(5)

$F_{\text{OUT}}$ 的变化范围在 1 Hz~70 kHz。

图 7 V/F 转换电路

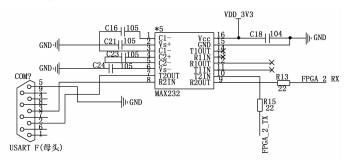

#### 1.7 串口发送电路

FPGA 将加速度计采集的信号通过 RS232 串口发送至上位机,从而比较 A/D 采集系统与 I/F 采集系统的优劣。 RS232 采用负逻辑进行传送数据,规定逻辑 "1"的电平为 -5 V~-15 V,逻辑 "0"的电平为+5 V~+15 V。选用该电气标准的目的在于提高抗干扰能力,增大通信距离 [ $^{19}$ ]。 系统采用 MAX232 作为传输芯片,芯片的第 7 引脚 T2OUT 与 DB9 的第 2 引脚 RX 端相连,芯片的第 8 引脚 R2IN 端与 DB9 的第 3 引脚 TX 端相连,从而完成 FPGA 与上位机的 串口通信。串口发送电路如图 8 所示。

图 8 串口发送电路

#### 2 系统软件设计

FPGA程序是在 Vivado 中通过 Verilog 语言编写完成的<sup>[10]</sup>。采用 A/D 控制模块以及 I/F 处理模块分别同时对两路加速度计信号进行采样,然后将处理的数据有序存储在FIFO 模块中,等 FIFO 模块存储的数量满足一定条件时,将 FIFO 模块中的数据有序读到编帧模块中,通过编帧模块,从而区分加速度计 1 信号与加速度计 2 信号,最后,将编帧好的数据通过 RS232 串口发送到上位机。

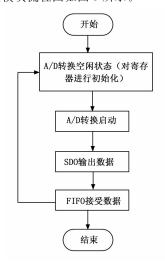

#### 2.1 A/D 控制模块

系统中 A/D 控制模块采用状态机进行时序控制,状态机分为 4 个状态,分别为空闲状态、A/D 转换状态、数据获取状态、数据输出状态 4 个状态[11]。A/D 的采样速率为300 kHz,采样时钟频率是由系统时钟频率 50 MHz 通过 5 分频得来的。A/D 在空闲状态时,分别让 AD7693 芯片CNV 端的信号拉低,让 SDI 端置成高电平,对转换计数的寄存器置零,对获取 A/D数据个数的寄存器置零;在 A/D转换状态,将 CNV 端置高,并对 CNV 端所处高电平的时间进行计数,当高电平所处时间达到 3 μs 时,将 CNV 端拉

低,并将状态跳转到数据获取状态;在数据获取状态,获取 A/D转换的时钟周期为 20 ns,通过 SDO 端将 A/D转换的数据存储到 FPGA 的临时存储器中,等 16 位数据全部存储到临时存储器中时,状态跳转到数据输出状态;在数据输出状态,将临时存数器存储的 A/D转换数据输入到 FIFO控制模块中,从而供 FIFO 控制模块对其进行编帧处理。A/D转换控制模块流程图如图 9 所示。

图 9 A/D 转换控制模块流程图

#### 2.2 I/F 处理模块

由于 I/F 模块输出的频率范围是 1  $Hz\sim70$  kHz, 系统的时钟频率为 50 MHz, 可以满足对 I/F 模块输出的频率进行采样。

为了测得 I/F 采集电路采集的频率,需要根据特定的办 法进行频率测量,一般的频率测量方法分为:周期测量法 和频率测量法 $^{[12]}$ 。周期测量法是根据  $f=rac{1}{T}$  测出被测信号 的频率,将基准信号作为参考,测得一个被测信号周期所 需基准信号周期的个数,从而测得一个被测信号周期所需 的时间,从而根据理论公式测得被测信号的频率;频率测 量法以基准信号为参考,在一定时间范围内,对被测信号 的周期个数计数,根据  $\frac{1}{f_s} \times N_x = \frac{1}{f} \times N_s$  可得被测信号的 频率。根据上述两种测得被测信号频率的方法,虽然可以 测得被测信号的频率,但存在±1个被测脉冲的误差,对测 量结果容易产生巨大影响,在实际中应用甚微[13]。根据上 述两种测量方法可知,周期测量法适用于测量低频信号; 而频率测量法适用于测量高频信号, 但两者不能同时满足 高低频率信号测量精度的要求,为了满足本系统采集高低 频率精度的要求,本系统提出采用等精度测频法,该方法 是利用一个与被测信号有关的门控信号来测得被测信号的 频率,门控信号的门阀时间正好是被测信号周期的整数倍, 根据  $\frac{1}{f_s} \times N_x = \frac{1}{f_s} \times N_s$  得,在门控时间内,对基准信号周 期的个数进行计数,从而测得门控时间;同时对被测信号

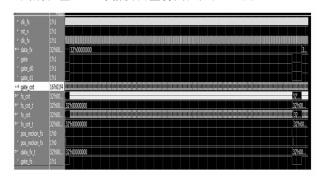

的个数进行计数,根据公式可得被测信号的频率。由于门控信号的门阀时间正好是被测信号周期的整数倍,从而测量的结果误差与被测信号无关,从而消除对被测信号产生±1周期误差<sup>[14]</sup>。等精度测量仿真图如图 10 所示。

图 10 等精度测量仿真图

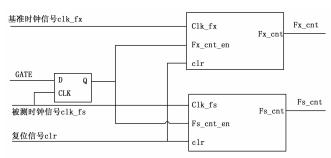

等精度测频系统的 RTL 图如图 11 所示。先初始化,基准时钟信号  $clk_-fx$  的频率为 50 MHz,基准时钟信号计数器  $F_{s_-}cnt$  为 0,门控信号 GATE 为 0,被测信号计数器  $F_{s_-}cnt$  为 0,门控信号 GATE 为 0,被测信号计数器  $F_{s_-}cnt$  为 0。为了避免 FPGA 内部触发器发生亚稳态,需要对输入的被测信号打两拍,从而能使 FPGA 能够精确的检测到被测信号的上升沿,当 FPGA 检测到被测信号的上升沿时,开始使门控信号 GATE 使能,从而使基准使能信号  $F_{s_-}cnt_-en$  和被测使能信号  $F_{s_-}cnt_-en$  使能,基准信号计数器  $F_{s_-}cnt_-en$  和被测信号计数器  $F_{s_-}cnt_-en$  种的计数,为了提高被测信号的精度,系统提高门控信号的使能时间,从而降低基准信号对被测信号精度的影响[15]。当门控使能信号达到一定时间时,将门控使能信号 GATE 拉低,然后获取基准信号计数器  $F_{s_-}cnt_-en$  的计数值,从而根据公式:

图 11 等精度测频系统的 RTL 图

$$\frac{fs - cnt}{clk - fs} = GATE - TIME = \frac{fx - cnt}{clk - fx}$$

(6)

由此推出:

$$clk _fx = F_x _cnt \times \frac{clk _fs}{F_s _cnt}$$

(7)

从而得出被测信号的频率值,根据被测信号频率的变化,以此来判断加速度计的变化。

#### 2.3 编帧模块

由于采集的数据是两路加速度计的信号,为了使加速

度计输出信号便于 FPGA 处理以及在串口调试助手后便于数据分析,需要将两路数据进行适当编码<sup>[16]</sup>,从而能够通过串口调试助手分析两路加速度计的变化情况。2 路数据帧结构如表 1 所示。

表1 2路数据帧结构

| 信号    | 数据大小(字节) | 编帧   |

|-------|----------|------|

| 帧头    | 2        | 90BE |

| 加速度1  | 2        | XX   |

| 加速度 2 | 2        | XX   |

| 帧尾    | 2        | EB09 |

#### 3 测试结果及分析

系统采用的石英挠性加速度计的测量范围在 15~g,偏值小于 5~mg,温度系数小于  $30~\mu g$ /  $\mathbb C$ 。采用离心机对两个石英挠性加速度计在相同环境下进行摆动测试。表 2~ 为石英挠性加速度计 A/D 采集数据,表 3~ 位石英挠性加速度计 I/F 采集数据。

表 2 石英挠性加速度计 A/D 采集数据

| 加速度/g | 输出电压/V   |

|-------|----------|

| -15   | 4.935    |

| -10   | 4.085    |

| -5    | 3.396    |

| 0     | 2.521    |

| 5     | 1.632    |

| 10    | 0.954    |

| 15    | 0.0184   |

|       | <u> </u> |

表 3 石英挠性加速度计 I/F 采集数据

| 69.996K |

|---------|

|         |

| 59.965K |

| 48.865K |

| 33.906K |

| 28.852K |

| 10.165K |

| 100     |

|         |

由上述两表可知, I/F 采集系统和 A/D 采集系统在相同条件下, 当离心机使两个挠性加速度计都处于—15 g的情况下, 理论情况下, 由两者采集系统的理论公式可得, A/D 采集系统采集的电压为 5 V, I/F 采集系统输出的频率为 70 kHz, 由表可知, 实际情况下, A/D 采集系统采集的电压为 4.935 V, I/F 采集系统采集的频率为 69.996 kHz, 可得转换两者的转换精度分别为 98.7%和 99.99%; 当离心机是两个挠性及速度计都处于 10 g的情况下, 理论情况下, 由两者采集系统的理论公式可得, A/D 采集系统采集的电

压为 1 V, I/F 采集系统输出的频率为 10 kHz, 由表可知,实际情况下,A/D 采集系统采集的电压为 0.954 V, I/F 采集系统采集的频率为 10.165 kHz, 可得转换两者的转换精度分别为 95.4% 和 98.38%; 并且 I/F 采集系统采集频率的范围是  $1 \text{ Hz} \sim 70 \text{ kHz}$ , A/D 采集系统采集的电压范围是  $0.001 \sim 5 \text{ V}$ , 所以 I/F 采集的数据变化范围大,精度更高,灵敏度更好。

#### 4 结束语

通过对石英挠性加速度计 A/D 采集系统和 I/F 采集系统的对比研究,分别从硬件模块和软件模块两方面对测试系统进行全面阐述。通过在串口调试助手上观察数据变化,结果证明 I/F 采集系统占用资源少,采集数据灵敏度高,精度高,易用于寻北仪导航系统的测试。

#### 参考文献:

- [1] 陈 浩. 基于 ARM 的石英挠性加速度计采集处理系统设计 [D]. 哈尔滨:哈尔滨工程大学,2007.

- [2] 张建伟, 陆亨立. 硬件描述语言与数字逻辑电路设计 [J]. 电子工程师, 1999 (4): 3-5.

- [3] 徐 欣,于红旗,卢启中."嵌入式系统设计技术"课程教学研讨[J].高等教育研究学报,2004(2):59-60.

- [4] 宋雪杰, 赵 毅, 王晓东. 石英挠性加速度计 I/F 转换电路软件补偿研究 [J]. 导航与控制, 2010 (2): 52-55.

- [5] 程远超, 黄 伟, 赵新强, 等. 基于 FPGA 的大比例系数高精度 I/F 电路设计 [J]. 导航与控制, 2018, 17 (2): 59-66.

- [6] 张志文,范大海. 电流/频率转换电路综合测试系统研究 [J]. 仪表技术与传感器,2016 (2): 69-71.

- [7] 赵振涌, 袁 寰. 高精度 A/D 转换技术在惯导系统中的应用研究「J7. 导航定位与授时, 2014, 1 (2): 70-73.

- [8] 刘书凯. 单电源 I/F 转换电路设计 [J]. 电子科技,2011,24 (1):106-108.

- [9] 韩 巍,张立新,孟祥凯. VF 转换的特点及其应用 [J]. 工程与试验,2017,57(2):96-98.

- [10] 丁 聪, 胡宇航, 吴 婷, 等. 等精度频率计的 Verilog 设计与仿真[J]. 电子制作, 2020 (17): 22-23.

- [11] 邱学武. 基于以太网的高精度模数转换模块的研究 [J]. 信息与电脑(理论版), 2017 (24): 171-172.

- [12] 黄武扬,吴 一,黎 坤. 基于 I/F+A/D 的高分辨率模数 转换电路 [J]. 仪表技术与传感器,2020 (1): 108-111.

- [13] 范苗苗. I/F 放大变换电路测试系统研制 [D]. 西安: 西安工业大学, 2014.

- [14] 牛清红,张春熹,宋凝芳.用 A/D和 FPGA 实现的加速度计数据读出系统[J].中国惯性技术学报,2006(1):63-66.

- [15] 屠晓伟, 高志龙, 杨庆华. 基于 V/F 转换的多路信号远距离 传输系统设计 [J]. 自动化仪表, 2020, 41 (4): 98-101.

- [16] 韩 巍,张立新,孟祥凯. VF 转换的特点及其应用 [J]. 工程与试验,2017,57(2):96-98.