文章编号:1671-4598(2014)09-3081-03

中图分类号: TP334.7

文献标识码:A

# 基于 FPGA 的对击锤力能参数测量仪设计

## 王 鹏、睢 希、吕志刚

(西安工业大学 电子信息工程学院,西安 710068)

摘要:为实现在锻造生产中对击锤打击能量、打击力等力能参数的测量,设计了一种基于 FPGA 与 USB2.0 的四通道、高速同步数据采集系统;硬件采用两个压电式加速度传感器和两个位移传感器,FPGA 选用 Altera 公司的 EP2C5Q240I8,通过对打击过程中 524 ms内的加速度和位移数据的采集,计算出力能参数,并通过 USB2.0 将数据实时上传到 PC 机进行处理;重点介绍系统硬件电路设计、USB2.0 控制逻辑和 FPGA 内部状态机模块设计;系统采样频率达到1 MHz,数据传输速率达到30 MB/s,现场测试证明,该系统能够在强冲击、大振动环境下稳定可靠工作,为锻造质量控制提供了可靠的科学依据。

关键词:对击锤;力能参数;CY7C68013A芯片;USB2.0;FPGA

# Design of Counter—blow Hammer Energy Parameters Measuring Instrument Based on FPGA

Wang Peng, Ju Xi, Lü Zhigang

(School of Electronic and Information Engineering, Xi'an Technological University, Xi'an 710032, China)

Abstract: To achieve in the forging production parameter measurement of hammer blow energy, blow force and other force, design a kind of four channels, based on FPGA and USB2.0 high—speed synchronous data acquisition system. The hardware uses two piezoelectric acceleration sensor and displacement sensor, uses Altera FPGA EP2C5Q24018, based on the hit within 524 ms of acceleration and displacement in the process of the value of the collection, calculation can output parameters, and real—time uploaded to PC through USB2.0 data for processing. This paper introduces the system hardware circuit design, USB2.0 control logic and the FPGA internal state desktop module design. The system sampling frequency reaches 1MHz, the data transmission rate reaches 30Mb/s. Field test indicates that the system can in strong shock, vibration environment is stable and reliable work, the quality control of forging provide reliable scientific basis.

Keywords: counter-blow hammer; energy parameters; CY7C68013A; USB2.0; FPGA

### 0 引言

对击锤锻造过程中,打击能量是锻造成形时需要控制的关键参数,该参数的准确性测量是锻造过程质量控制和设备正常运行的必要条件。针对传统的测量测试方法中需要在现场布置大量的仪器设备、无法满足连续生产过程的测试要求。为了掌握该设备的性能和量化打击过程中的功能变化,决定设计一套先进的打击能量参数的自动采集与处理系统,可以满足在高温、高振动、高粉尘的恶劣环境下工作,并且采集打击过程中的瞬时速度和加速度,从而计算出打击力和打击能量,为现场工人对锻造质量控制和设备安全运行提供了可靠的科学依据。本文设计了一种基于 USB2.0 的多通道高速数据采集系统,重点阐述了下位机原理及软硬件设计。

#### 1 系统设计方案

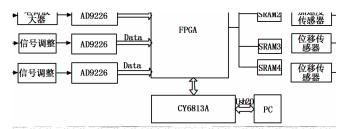

本系统采用 FPGA 作为核心控制芯片,为了保证采集系统的实时性和大容量要求,采用 512 k 容量的 SRAM 作为数据缓冲存储器,采用高速 AD9226 模数转换器,采用 USB2.0 来实现数据的传输,USB 接口芯片采用 CYPRESS 公司的 CY7C68013A,通过对其可编程逻辑接口 (GPIF)和内部 FIFO 存储器的合理设计,并配合外围逻辑器件以及 A/D 转换

收稿日期:2014-03-22; 修回日期:2014-04-17。

基金项目: 陕西省科技厅工业攻关项目(2013K07-15); 陕西省教育厅专项科研计划资助项目(11JK0921)。

**作者简介:**王 鹏(1978-),男,副教授,硕导,主要从事嵌入式系统应用、图像处理与机器视觉方向的研究。

器的有效运用,实现了高速的数据通信<sup>[1]</sup>。图 1 为系统总体设计框图。

图 1 系统结构框图

加速度和位移作为打击能量的关键参数,分别选用压电式加速度传感器和位移传感器,对传感器输出信号进行调理放大后,接入高速 A/D 的模拟输入通道,A/D 转换后的数据由 FPGA 芯片进行控制并存储到片外存储器 SRAM 中,在打击完成后,FPGA 对多路数据进行排序写入 USB 芯片 FIFO缓存,当 FIFO 数据达到满状态后,自动打包上传到 PC机上[2]。

#### 2 硬件电路设计

#### 2.1 AD9226 控制模块接口设计

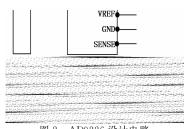

传感器输出信号经过信号调理放大电路后,转化为模拟电压量,A/D转换部分使用 AD9226 芯片,单电源供电,12 位

精度,功耗低(475 mV)最高采样率可以达到65 Msps,附加 一位溢出指标位,和较高的信噪比(69 db)。FPGA采用48 MHz 有源晶振作为输入时钟信号源, 经分频得到 1 MHz 采样 时钟,即1 μs 采样周期。硬件设计采用 FPGA 对 AD9226 逻 辑采样进行控制,具体电路如图 2 所示,本系统将 AD9226 配 置为单端输入的工作模式, VINA 端接模拟输入电压, SENSE 接口接地,内部 AD9226 的参考电压 VREF 配置为 2 V, VINB 端接 VREF, VINB 端接入+2 V的偏执电压,模拟电 压的输入范围是 0~3 V。

图 2 AD9226 设计电路

#### 2.2 SRAM 数据存储模块设计

由于 FPGA 芯片内部存储器的容量小,为了满足系统设 计的要求,数据存储部分采用片外异步高速存储器 IS61LV51216 完成对数据的大容量存储,它的存储容量 512 kbyte×16位数据, SRAM 数据写满的时间为 524.288 ms, 鉴于 FPGA 片内逻辑可以并行执行的特点,多路 A/D 信号并 行数据采集,可将各组数据分别写入对应 SRAM 芯片中,系 统设计了四路数据采集通道,并设计了4片 SRAM 作为缓存, 将 4 片 SRAM 芯片的地址线和数据线并联使用,每片 SRAM 的片选端口由 FPGA 分别控制,从而实现多片存储器级联的 并行工作, 达到高速存储, 同步的技术要求。

#### 2.3 USB 控制模块接口设计

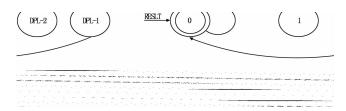

USB 数据传输部分选用 Cypress 公司 EZ-USB FX2LP 系 列 USB 芯片中 CY7C68013A, 该控制器, 主要包括 USB 2.0 收发器、串行引擎 (SIE)、通用可编程接口 (GPIF)、增强型 8051 内核、FIFO 存储器、I/ O接口、数据和地址总线。本设 计将 PC 机的 USB2.0 接口转换为一个透明的并行总线数据传 输接口,完全屏蔽了复杂的 USB2.0 协议,方便的跟 FPGA 外 部控制器连接。本设计的高速 USB2.0 数据传输模块有效数据 实时稳定传输速度达 30 Mbyte/s。FX2LP 可配置为主机 GPIF 模式或 slave FIFO 从机模式,本设计配置为从机模式,不考 虑 USB2.0 复杂的协议,将 USB 控制器作为一个 FIFO, USB2.0协议规则可以由芯片内部复杂的各种寄存器来设置。 FPGA 与 CY7C68013A 设计接口如图 3 所示。其中 FLAGA~ FLAGD 为 FIFO 的空、满的标志位,表示 FIFO 的控制状态, FX\_D [15:0] 为 FIFO 的双向数据端口, 低电平有效, FX \_A[1:0]为FIFO输入输出的地址端口,SLOE作为使能 信号 SLRD, SLWR 分别作为 FIFO 的读写信号[3-4]。

#### 系统控制软件设计

#### 3.1 USB 控制模块设计

状态机设计是数字电路设计中的一种重要方法, FPGA 逻 辑设计使用 Verilog HDL 硬件描述语言进行状态机设计。和以 往的 USB 传输引擎不同的是, FPGA 直接控制 FX2 内部 FIFO 以及传输,控制部分完全和传输模块脱离,很大程度上提高了

图 3 FPGA 与 CY7C68013A 硬件连接图

总线传输的速度,数据从 SRAM 中读出写入到 CY7C68013A 的 FIFO 中,内部的数据传输控制是通过两个控制信号来完成 的,分别是满标志 full 和空标志 empty,当 full=true 时不能 写数据,当 empty= true 时不能对 FIFO 进行读,将这个 full 信号作为 SRAM 的控制信号, 当 full 为 0 和 SRAM 写地址为 3ffff, 才可以将数据写入 FIFO[5]。

图 4 USB 同步读写状态机

本设计选用 ALTERA 公司的 Cyclone II 工业级芯片 EP2C5Q240I8, 采用 Slave FIFO 从机方式,实现对 CY7C68013A 的控制。其中 USB 同步读写状态机如图 4 所示: 初始化状态进行读写检测[6]。

如果写使能 FLAGA=1 时,FIFO 指针指向输入端点,地 址端地址 FIFOADR [1:0] =00, 同时如果 FLAGB=0, 即 FIFO 写满标志位为假,将外部数据写入 FD 当中,同时 SLOE =0, SLWR=1。同时给 SRAM 一个读使能信号 wrreq=1; 如果读使能信号 FLAGC=0 时,分配地址端地址 FIFOADR [1:0] =10. 这时 FIFO 指针指向输出端点。同时 FLAGD= 0,即 FIFO 读空标志位为假,将双向 FD 数据总线挂载在输出 状态,同时 SLOE=1, SLRD=1。为了保证状态机的稳定, 对系统进行两拍的锁存[7]。

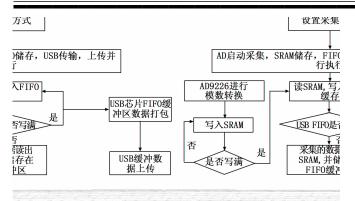

#### 3.2 高速数据采集系统设计

多路高速数据采集系统由下位机硬件与上位机软件组 成,下位机是由4路并行AD,FPGA芯片,4片SRAM和 USB 控制芯片构成,系统采集数据处理软件组成上位机设 计, FPGA负责对 A/D 模数转换, SRAM 存储和 USB 芯片 接口的控制,上位机完成数据通信握手设计,进行 PC 机的 数据处理,图5为高速数据采集仪的总体控制流程[8]。系统 上电后,触发信号有效时,A/D开始启动转换,FPGA读取 A/D转换结果并存入相应的 SRAM 中,数据采集完成后,当 上位机通过 USB 接口下发上传命令时, FPGA 读取 SRAM 中 的数据,并通过 USB 接口传送给上位机,从而实现完整采集 控制流程。

#### 4 系统测试

在实际应用前,需要对下位机性能进行测试,在上位机上 用 VC++小 16.0 设计一个人机界面软件,采用 USB2.0 与下 位机进行通信,上位机可向下位机设备下发采集命令等控制,

图 5 高速数据采集系统的总体控制流程

并将采集到的数据进行可视化处理,测试选用一个波形发生器来产生模拟信号,选用一个正弦波,频率为 495 kHz,幅值为 2.3 V 作为模拟输入端的输入进行数据采集和分析,由于采样 频率为 1 MHz, SRAM 容量为 512 k,图 6 为上位机软件界面显示图,通过软件计算,得到采集后的信号频率为 494.812 MHz,准确性达到 99.9%,幅值为 2.295 V,准确性达到 99.7%,采样时间为 524 ms,从而验证了本系统数据采集的正确性和实时性。

#### 5 结束语

本文介绍了一种锻造行业中对击锤打击力能参数的高速数据采集系统,采用 FPGA 实现多路高速数据采集系统,硬件系统充分利用了 FPGA 丰富的 I/O 资源和强大的并行处理能力,选用高速 AD9226 作为 A/D 采样芯片,SRAM 作为数据缓冲存储器,USB2.0 作为数据高速传输方式,实现了系统并行、大容量、并行的技术要求,单通道采样速率可以达到 1 MHz,USB 总线将采集到的数据批量打包实时上传到上位机,传输速率可以达到 30 MB/s,该采集系统的硬件接口简单,采集速率高、功耗低,精度高,可以很方便的应用于其他行业数据采集系统中,通过更换不同的传感器,可以应用于不同场合的测控需要。

#### 参考文献:

- [1] 李 亭, 李 华. GPIF 与 FIFO 接口设计 [J]. 电测与仪表, 2006, 43 (6): 56-58.

- [2] 王 宇, 任晓红, 张 超, 等. 基于 FPGA 的交流采样同步倍频 算法及实现[J]. 电测与仪表, 2013, (12): 47-50.

- [3] 高迎慧, 候忠霞. 基于 FPGA 和 USB 的高速数据采集与传输系统 [J]. 工矿自动化, 2007, 4 (8): 105-106.

- [4] 焦斌亮, 韩志学. 基于 EZ-USB FX2 实现的高速数据采集系统 [J]. 仪表技术与传感器, 2005, (7): 21-22.

- [5] 谭安菊, 龚 彬. USB2.0 控制器 CY7C68013 与 FPGA 接口的 Verilog HDL 实现 [J]. 电子工程师, 2007, 33 (7): 52-55.

- [6] 曾 虹,刘世杰,张 翔,等. 基于 USB 的高速并行数据采集系统的设计与实现 [J]. 计算机测量与控制,2007,15(8):1105-1106.

- [7] 刘 吉,杨德伟,文怀涛,等. 基于 USB 通信的 FPGA 高速数据采集系统[J]. 现代电子技术,2011,34 (10):186-192.

- [8] 安 荣,任勇峰,李圣昆.基于 FPGA 和 USB2.0 的数据采集系统 [J]. 仪表技术与传感器,2009,(3):49-51.

#### (上接第 3076 页)

量机构建传感器输入输出特性的回归拟合模型,模型的参数向量由量子粒子群优化算法与平均绝对误差最小的准则进行自适应优化。实验结果验证了该方法的有效性,其模型的拟合性能明显高常规方法,对传感器非线性特性研究具有较好参考价值。

#### 参考文献:

- [1] 马迎坤, 张希农. 多维传感器标定的支持向量机复合式方法 [J]. 航空动力学报, 2011, 26 (6): 1274-1281.

- [2] 程德福,王 君,凌振宝,等,传感器原理及应用[M].北京: 机械工业出版社,2013.

- [3] 简弃非,刘海燕. SnO2 纳米传感器灵敏度-温度特性曲线拟合研究[J]. 传感技术学报,2005,18 (1):50-52.

- [4] 陈坤华,卢文科. 载体催化型瓦斯传感器输出电压与瓦斯何种分数函数关系研究[J]. 工矿自动化,2013,39(2):92-95.

- [5] 曾喆昭, 竺 炜, 孙湘海, 等. 一种基于神经网络算法的高精度拟合传感器温度特性曲线的方法 [J]. 传感技术学报,2007,20 (2): 326-328.

- [6]徐萃薇. 计算方法引论 [M]. 北京: 高等教育出版社, 2001.

- [7] 黄为勇, 童敏明, 任子晖. 热导传感器温度特性的 CPSO-SVM 数据融合校正 [J]. 计算机应用, 2009, 29 (12): 3259-3262.

- [8] 孙 林,杨世元. 基于 LS-SVM 的温度传感器非线性关系拟合及 参考端温度补偿 [J]. 应用科学学报, 2009, 27 (6): 616-622.

- [9] 闰俊荣,郭西进. 基于最小二乘支持向量机的异步电机转子故障诊断[J]. 计算机测量与控制,2013,21(2):336-339.

- [10] Isis Didier Lins, Márcio das Chagas Moura, Enrico Zio, etc. A particle swarm optimized support vector machine for reliability prediction [J]. Quality and Reliability Engineering International, 2012, 28 (2): 141-258.

- [11] Bergh F V D. An Analysis of Particle Swarm Optimizers [D]. Pretoria: University of Pretoria, 2001.

- [12] Sun J, Feng B, Xu W B. Particle swarm optimization with particles having quantum behavior [A]. IEEE Proc of Congress on Evolutionary Computation [C]. Piscataway: IEEE, 2004: 325-331.

- [13] 孙 俊,方 伟,吴小俊,等. 量子行为粒子群优化:原理及其应用[M]. 北京:清华大学出版社,2011.

- [14] 张金玉,张 炜. 装备智能故障诊断与预测 [M]. 北京: 国防工业出版社,2013.