文章编号:1671-4598(2014)06-1912-03

中图分类号:TN972

文献标识码:A

# 雷达目标干扰调制信号的 FPGA 实现

## 梁清龙, 王建业, 岳鸿鹏

(空军工程大学 防空反导学院,西安 710051)

摘要:用 VHDL 语言在 Quartus II 环境下对雷达干扰调制信号的产生进行设计;将 FPGA 实现的功能分为数字噪声模块、调制波形模块和角度包络模块,详细给出设计过程;经过仿真和硬件测试,实现了雷达目标干扰调制信号的输出;研究表明该系统方便控制,容易修改,并且能移植到其它目标模拟器,对干扰调制信号的设计有一定的借鉴意义。

关键词: VHDL; 干扰调制; 数字噪声; 调制波形; 角度包络

## FPGA Implementation of Radar Target Jamming Modulation Signal

Liang Qinglong, Wang Jianye, Yue Hongpeng

(Missile Institute, Air Force Engineering University, Xi'an 710051, China)

Abstract: Radar target jamming modulation signal is designed by VHDL language under the environment of Quartus II. The function of FPGA is divided into three units with the detailed design process, including digital noise unit, modulation waveform unit, angle envelope unit. Through the simulation and hardware test, radar target jamming modulation signal is generated successfully, research shows that the system is convenient to control, easy to modify, and can be transplanted to other target simulator, it also has certain reference significance to the design of the jamming modulation signal.

Key words: VHDL; jamming modulation; digital noise; modulation waveform; angle envelope

### 0 引言

近年来,伴随着计算机科学、微电子学等相关技术的发展 以及实践需求,各种雷达模拟器的发展极为迅速。国内外对雷 达目标模拟器的研究大多采用了软硬件相结合的设计方式, 使 系统在有很大的灵活性的同时也满足了信号实时输出的需要。 在雷达目标模拟器中、干扰环境产生是其重要组成部分、主要 模拟地物、气象杂波以及各种噪声。以往的文献中对干扰信号 的产生大多是理论上的论述并没有做系统全面的设计, 文献 [1] 中设计的模拟器对统计模型产生的杂波和噪声干扰信号存 入存储器,利用硬件控制逻辑完成数据的读取;文献[2]对 雷达目标回波信号进行详细分析,以目标回波信号为主,系统 噪声信号在设计时直接采用系统自身噪声来代替;文献「3] 设计了一种稳定度高,通过改变信号源载频模拟目标频移的模 拟器,未对杂波和噪声进行考虑;文献[4]将杂波数据预先 存放在存储卡中,干扰信号的包络数据从 RAM 中读出之后不 进行距离信号选通, 而是与杂波数据进行相乘调制然后再与均 勾白噪声相乘进行调制,经过两次调制后可实现对不同于批信 号的模拟,但设计过程未做具体介绍。

本文依据文献 [4] 的启发,设计了一干扰调制器,对干扰信号的产生及调制进行了具体分析,利用 FPGA 分别产生高斯白噪声、干扰调制波形和角度包络信号,经过一系列的调

制最后输出干扰调制信号,通过改变 FPGA 配置数据或修改程序可以产生其他复杂干扰波形,并且能方便地移植到其他雷达模拟器的电路设计当中。

## 1 干扰调制器方案设计

#### 1.1 设计要求

该雷达目标干扰调制器的主要技术指标如下:

- (1) 产生的噪声为高斯白噪声;

- (2) 产生4种干扰调制波: 钟形包络、锯齿波、三角波、方波:

- (3) 产生具有方位角为和高低角的包络信号;

- (4) 输出干扰调制信号。

#### 1.2 系统结构设计

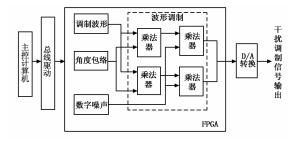

按照技术指标,整个系统以 FPGA 为核心,产生的两路独立的包含角度信息的干扰调制信号。干扰调制信号生成原理如图 1 所示,其 FPGA 部分主要由数字噪声产生模块、调制波形产生模块以及角度包络产生模块组成。

图 1 干扰调制信号原理框图

雷达目标回波信号的组成比较复杂,除目标信号外,要考

收稿日期:2013-11-27; 修回日期:2014-01-13。

作者简介:梁清龙(1989-),男,山东垦利人,硕士,主要从事微电子 技术在武器系统中的应用方向的研究。

王建业(1962-),男,陕西耀县人,教授,主要从事微电子技术在武器系统中的应用方向的研究。

虑噪声和杂波。调制波形模块产生的是干扰调制信号来模拟杂波; 角度包络模块产生分别带有高低角和方位角干扰包络信号, 用来和干扰信号相乘调制; 数字噪声模块主要产生高斯白噪声,模拟系统自身噪声。三大模块产生信号经波形调制(两级乘法器)后,最后输出干扰调制信号。

## 2 干扰调制信号的 FPGA 实现

#### 2.1 数字噪声模块

此模块采用线性反馈移位寄存器<sup>[5]</sup>(Linear Feedback Shift Register, LFSR)方法产生均匀分布的白噪声,通过修改程序即可得到所需的噪声参数,扩展性和移植性大大加强。LFSR 是用来生成二进制伪随机序列的一种手段,其工作原理是:首先给寄存器基本存储单负初值,当控制寄存器的时钟的每一个时钟节拍到来时,基本存储单元的值右移一位,基本存储单元的值的一个子集异或后反馈到最左边的单元,在这个更新的过程中,可以获得一个位的输出<sup>[6]</sup>。

LFSR 所产生的伪随机序列称 m 序列,假设一个 LFSR 长度为 n,那么其内部状态最多为  $2^n$ ,因为 "0" 状态是全封闭的,因此它的周期最大为  $2^n-1$ 。在实际应用中我们可以通过查表来确定所需的质数多项式。从 m 序列中抽头组成的二进制序列满足白噪声的定义,且 m 序列的噪声特性与其周期长度有关,理论上讲,周期越长越接近白噪声谱<sup>[7]</sup>。在实际应用中,因为 FPGA 的硬件资源是有限的,所以周期不能任意长,本设计选用周期为  $2^{25}-1$  的 m 序列,查表得其质数多项式  $f(x) = x^{25} + x^3 + 1$ ,该 m 序列发生器用 VHDL 语言实现。

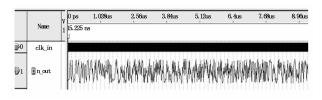

系统设计需要的是高斯白噪声,因此还需将 m 序列得到均匀分布的白噪声进行转化。将均匀白噪声转换成高斯白噪声一般用地址法和公式法。地址法用的是两者的映射关系;公式法依据中心极限定理, $x=\sqrt{\frac{12}{n}}(\sum_{i=1}^n r_i - \frac{n}{2})$ ,当 n 足够大时,对近似可得近高斯分布 N (0,1)。考虑到雷达模拟器中对实时性的高要求,本设计采用地址法最佳。具体方法是在 ROM中存入高斯噪声表,再用均匀白色功率谱随机序列作为地址输入,直接寻址,并行计算<sup>[8]</sup>,读取相应单元存储的数据,输出即为高斯白噪声,其仿真结果如图 2 所示。

图 2 高斯白噪声时序仿真图

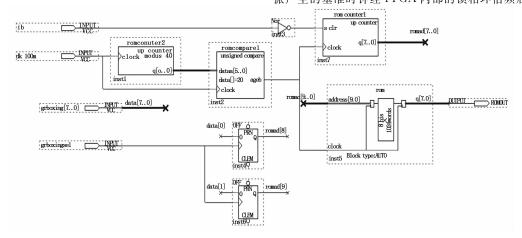

#### 2.2 调制波形模块

根据系统设计要求,产生4种干扰调制波:钟形包络、锯齿波、三角波和方波。调制波形产生模块主要由地址发生器、ROM以及波形选择电路3部分组成。其中,ROM分地址段存储着4种波形,而地址发生器和波形选择电路共同形成ROM的地址。在主控计算机送来的波形选择信号控制下,该模块可以完成对所需要产生的调制波形数据的选择、读取和输出。调制波形模块实现的电路图如图3所示。

图 3 中 ROM 地址产生计数器的时钟由 100 MHz 时钟分 频后得到,存储着 4 种波形数据的 ROM 存储深度为 1 024,地址线为 10 位。但地址计数器只负责产生读 ROM 地址的低 8 位,负责选择何种波形输出的高两位的地址由主控计算机在角同步信号的低电平期间写入。高两位的地址为 00 时,输出钟形包络;高两位的地址 01 时,输出锯齿波;高两位的地址 10 时,输出方波;高两位的地址 11 时,输出三角波。

#### 2.3 角度包络模块

根据系统设计要求,这里需要产生两个独立的角度包络信号(均携带有高低角和方位角信息)来和干扰噪声进行乘法调制。和方位角角度包络产生的原理与目标信号的角度包络产生原理一致,方位角计数器对时钟进行计数,当计到主控计算机预先送来的高低角(方位角)偏移值时送出一个地址产生使能信号到包络地址产生器,地址产生器生成的地址与计数脉冲分频产生的ROM读时钟协同控制,使ROM里存储的角度包络数据被逐一读出。

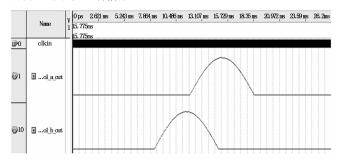

假定方位角为 60°, 高低角为 30°, 其时序仿真结果如图 4 所示。

#### 2.4 干扰调制包络信号生成

为保证系统能正常工作,必须要有各同步信号。由外部晶振产生的基准时钟经 FPGA 内部的锁相环倍频后送至计数器,

图 3 调制波形产生电路结构图

经计数分频后再送至比较器进行波形、占空比调整便可得到计数时钟。距离同步信号和角度同步信号的模拟产生原理类似, 此部分用 VHDL 实现。

在设计得到上文中提到的高斯白噪声、调制波形、角度包络以及同步信号后,再对它们进行乘法调制便可得到干扰调制包络信号输出。干扰调制包络信号产生的电路由5部分组成,其中moni\_tb是同步信号产生模块,ganrao\_roml是调制波形产生模块,ganrao\_baoluo是角度包络产生模块,m\_xulie是数字噪声产生模块,它们的输出经两级乘法调制后便能得到所需要的干扰调制信号。

图 4 角包络信号产生时序仿真结果

## 3 设计结果分析

本设计采用的测试平台为 Altera DE2<sup>[9]</sup> 开发板,其核心 FPGA 芯片为 Cyclone II EP2C35F672C6,其硬件资源包含有 33216 个逻辑单元 LE, 105 个 M4K RAM 块,483 840 个 RAM 位,35 个嵌入式 18×18 乘法器,4 个锁相环,最大可用 I/O 管脚 475 个,205 个差分通道。将工程编译下载到开发板,并用示波器观察,经观察波形以及各项参数该系统达到了设计要求。

#### 4 结束语

本系统以 FPGA 为核心器件,以 VHDL 语言和原理图相结合的方法分别设计完成了高斯白噪声、调制波形和角度包络的模块,最后对各信号进行乘法调制实现了对雷达目标模拟器干扰调制部分的设计。通过 Altera DE2 硬件平台的测试,验证了设计可行性,干扰调制器内部各项参数修改方便,可进行实时配置,通用性强,便于移植到其它雷达目标干扰器中,对其他类型模拟器干扰调制部分的设计具有借鉴意义。

#### 参考文献:

- [1] 胡万坤,潘瑞云,沈 磊. 数字阵列雷达目标模拟器设计 [J]. 雷达与对抗, 2013, 33 (1): 46-50.

- [2] 李国民,张 茜,廖桂生.基于 FPGA 的雷达目标回波模拟器的设计与分析 [J]. 计算机测量与控制,2012,20 (11):2992-3010.

- [3] 马魁勇,于长军,位寅生. 基于 FPGA 的雷达目标模拟器的设计与实现[J]. 仪器仪表学报,2006,27 (6):870-872.

- [4] 路文龙, 王和明, 张启亮, 等. 基于 FPGA+PC104 的雷达目标模 拟器设计 [J]. 电子技术应用, 2012, 38 (4): 27-30.

- [5] Stahnke W. Primitive Binary Polynomials [J]. Mathematics of Computation, 1973: 977-980.

- [6] 岳鸿鹏, 王和明. 基于 DSP Builder 的改进型序列生成器设计 [J]. 计算机测量与控制, 2010, 18 (11): 2632-2637.

- [7] 蒋 乐, 冯文全. 高性能可编程高斯白噪声的设计与实现 [J]. 电子技术应用, 2006 (8): 113-115.

- [8] Lee D, Luk W. A hardware gaussian noise generator using the wallace method [J]. IEEE Transaction VLSI Systems, 2005, 13 (8): 911-920.

- [9] 张志刚. FPGA 与 SOPC 设计教程——DE2 实践 [M]. 西安: 西安里子科技大学出版社,2007.

#### (上接第 1907 页)

因 SD 卡读取数据的速度比写入速度要快,所以此处仅测试了 SD 卡存储数据的性能。具体的测试是在实验平台(一)所用实验参数的基础上进行的,测试参数与结果如表 2 所示。

表 2 测试参数

| 波特率<br>(kb/s) | 报文<br>接收数 | SD 卡<br>写入数 | 正确率 (%) |

|---------------|-----------|-------------|---------|

| 250           | 1 024     | 1 024       | 100     |

| 500           | 1 024     | 1 024       | 100     |

| 1 000         | 1 024     | 1 024       | 100     |

#### 5 结论

利用 XMC4500 单片机将虚拟串口技术、CAN 总线收发、SD 卡记录等功能高度集成化,提高了整个 CAN 卡的可靠性和抗干扰性。为汽车 CAN 网络检测、基于串口的软硬件系统提供了便捷的使用工具,灵活的配电方式也可以将其用于汽车的车载黑匣子,可以预见具有很好的应用前景。

#### 参考文献:

- [1] 范伟成,宗 情,朱辰元.基于单片机的 CAN-USB 通信转换模块的设计与实现 [J]. 计算机测量与控制,2012,20 (3):744-746

- [2] 俞卫芳,赵不贿,杨 鲲. 基于 USB 的 CAN 总线适配器的设计 [J]. 计算机测量与控制,2005,13 (11):1150-1152.

- [3] 宁 辉, 孙学艳, 刘 建, 等. VB6. 0 环境下基于 USB 的虚拟 串口通讯实现 [J]. 现代电子技术, 2012, 35 (6): 45-48.

- [4] 钱震宇, 肖昌汉, 李志新. 基于 51 单片机的 CAN 总线转串口通信卡的设计与实现 [J]. 船电技术, 2011, 31 (12): 32-34.

- [5] 沈 斌,秦宪礼,刘新蕾.基于虚拟串口技术的 CAN-bus 总线 在煤矿通讯中的应用研究 [J].煤炭技术,2008,(12):29-31.

- [6] 韦立明. 基于 USB 通信设备类的虚拟串口研究与设计 [D]. 西安电子科技大学,2012.

- [7] XMC4500 Microcontroller Series for Industrial Applications Reference Manual [Z]. V1. 1. Infineon Tehnologies AG, 2012.

- [8] 周 跃,沈 捷,花 魁. 基于 SD 卡的数据存储系统设计 [J]. 化工自动化及仪表, 2012, 39 (1): 95-98.